Im Auftrag der Bosch Car Multimedia hat die Custom Development Organisation von Zuken eine Lösung entwickelt, die eine Parallelisierung von IC-, Stecker- und PCB-Entwicklung durch automatisierte Aktualisierung der Pinbelegung im PCB-Design ermöglicht. Die Lösung liest Pin-Belegungslisten von SoC-Modulen oder vielpoligen Steckern in CR-8000 Design Gateway ein und legt automatisch alle erforderlichen Verbindungen, Busse und Hierarchieverknüpfungen im Schaltbild an. Dies ermöglicht eine erhebliche Reduktion von Aufwand und Fehleranfälligkeit bei der Aktualisierung der PCB-Designs.

Um den kurzen Innovationszyklen im Bereich Bordnetztechnologie gerecht zu werden, ist es erforderlich, die Entwicklungsstände von Steuergeräten, Steckern und elektronischen Baugruppen (sprich: Leiterplatten) so effizient wie möglich zu synchronisieren. Da sich mit wachsendem Funktionsumfang die Pinbelegung von Steuereinheiten und Steckern häufig ändert, ist es erforderlich, die Pinbelegung der betroffenen Elemente auf PCB-Seite regelmäßig zu aktualisieren.

Diese Aktualisierung möglichst weitgehend zu automatisieren und manuelle – und damit inhärent auch fehlergefährdete – Änderungen am PCB-Design möglichst zu vermeiden, war das Ziel einer Lösung, die Zuken im Auftrag von Bosch entwickelt hat. Diese ist seit kurzem unter der Bezeichnung Automatic Block Update, kurz ABU, erfolgreich in den Produktivbetrieb übernommen worden.

Automatic Block Update (ABU)

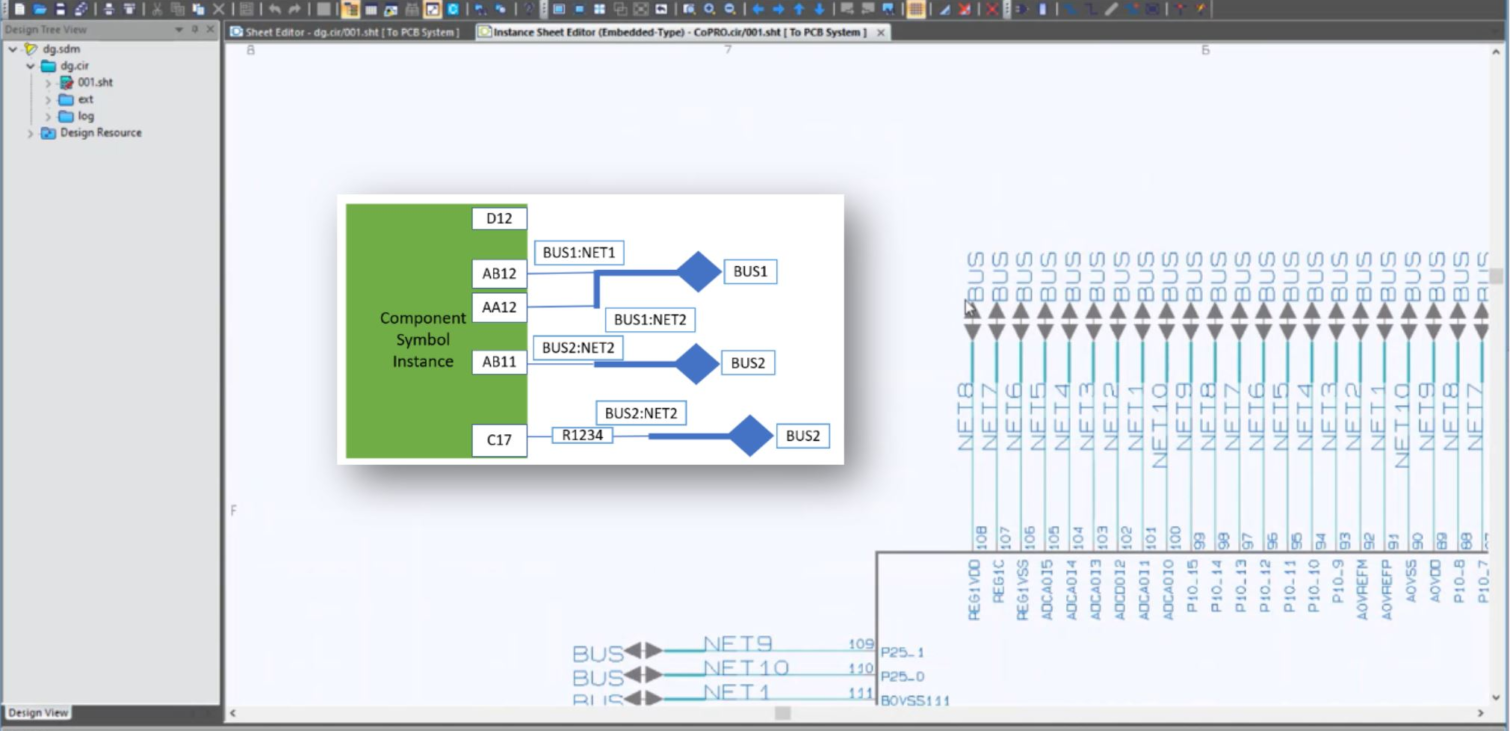

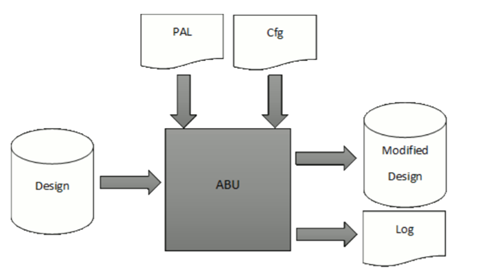

Die Funktionsweise von ABU kann wie folgt skizziert werden: Pin-Belegungslisten (in nachfolgender Illustration als PAL oder Pin Assignment List bezeichnet), die von der IC-Entwicklung in maschinenlesbarem Format bereitgestellt werden, werden über den Automatic Block Update in die CR-8000 Schaltungsentwicklungsumgebung Design Gateway von Zuken eingelesen und automatisch aktualisiert (Bild 1).

Der Automatic Block Update legt dabei in Design Gateway automatisch alle erforderlichen Verbindungen, Busanbindungen und hierarchischen Konnektoren an, die für die Verbindung zwischen den Blättern von hierarchischen Designs sorgen. Die Änderungen werden in mehreren Durchgängen auf allen Blättern und Ebenen des Design Gateway automatisch erzeugt. (Bild 1)

Netzanschlüsse, Busanschlüsse und Sheet Connector werden angelegt

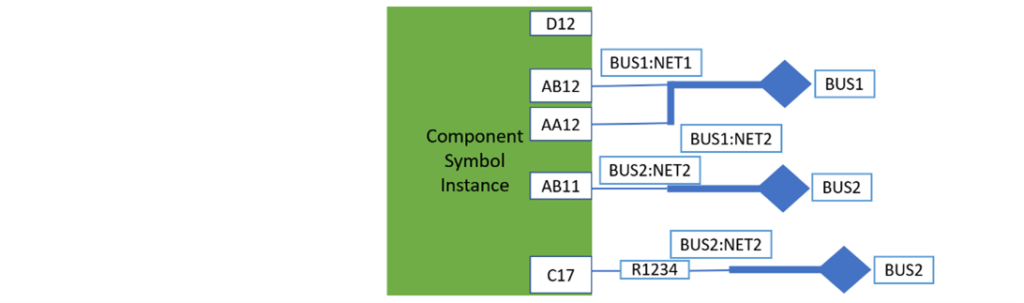

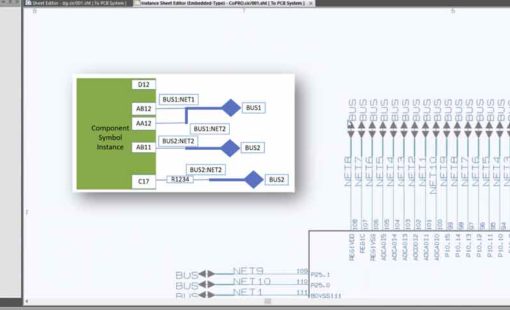

Für jeden Pin, der in dem IC-Baustein in Design Gateway (in der Grafik als grünes Rechteck dargestellt) noch nicht angeschlossen ist, werden in einem automatisierten Vorgang die erforderlichen Anschlüsse angelegt (Bild2):

- Der Netzanschluss (dünne blaue Linie)

- ein Busanschluss (dicke blaue Linie)

- und einen Sheet Connector (blaue Raute).

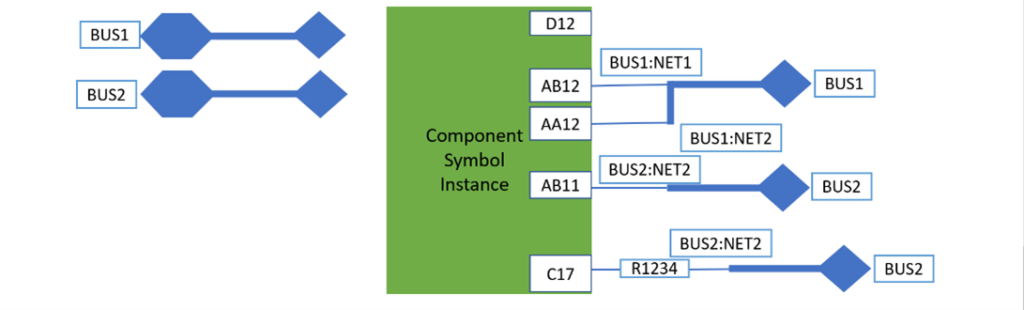

- Zusätzlich wird auf demselben Sheet, auf dem das IC-Symbol platziert ist, ein Hierarchie-Konnektor angelegt, mit dem der betroffene Bus mit der nächsthöheren Ebene verbunden werden kann (Bild 3).

Falls an einem IC-Symbol bereits ein Wire mit einem passiven Baustein angeschlossen ist, und dahinter bereits eine Net Bus Connector Group angelegt ist, werden die bereits vorhandenen Netze und Busanschlüsse über das Automatische Block Update vollautomatisch angepasst. Die bereits vorhandenen Netze werden automatisch umbenannt.

Alle Änderungen, die im Verlaufe des Block Updates am Schaltplan vorgenommen werden, werden in einer Protokolldatei dokumentiert und können über eine Undo-Funktion, falls erforderlich, auf den Ausgangszustand zurückgesetzt werden. Die Funktion kann wahlweise für den gesamten Entwurf oder für einen ausgewählten Block gestartet werden.

Vorteile einer automatisierten Aktualisierung der Pinbelegung

„Durch die Einführung von ABU konnte die PCB-Entwicklungszeit bei Bosch Car Multimedia deutlich verkürzt werden“, bestätigt Klaus von Treufels, Technical Director of HW-Architecture and System Design. „Gleichzeitig hilft ABU Schaltbildfehler, wie sie in manuell erstellten Schaltbildern unweigerlich auftreten, zu vermeiden.

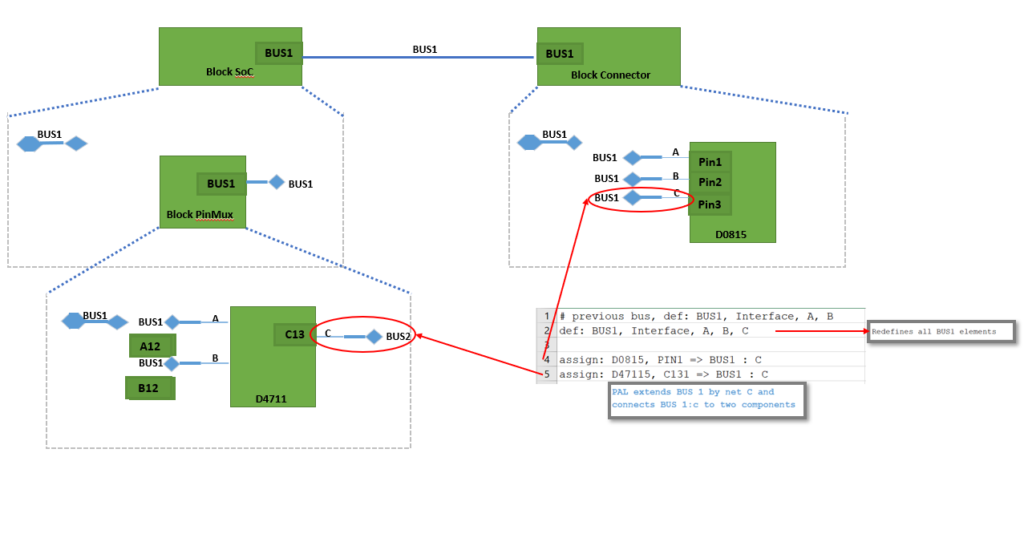

Da Quantifizierungen insofern problematisch sind, als sie in erheblichem Maße vom Umfang der zu bearbeitenden Schaltbilder abhängen, wurde ein Fallbeispiel zu Vergleichswecken einmal manuell und einmal mit ABU bearbeitet. Dabei sollten in einem Schaltbild typischer Komplexität zwei Schaltbildkomponenten (D4711, D0815) miteinander verbunden werden. Dazu wird ein schon existierender Bus (BUS1), welcher in diesem Fall über 3 Blockgrenzen hinweg verläuft, um ein Signal (BUS1:C) erweitert und dieses an die korrekten Pins der Bausteine angeschlossen (Bild4).

Bei der automatischen Bearbeitung mit ABU dauerte der gesamte Vorgang 5:17 Minuten, wobei 1:58 Min auf das Einlesen Schaltbildes entfielen und 3:19 Min auf das Zurückschreiben des Resultats der Aktualisierung in das Schaltbild entfielen. Der eigentliche Berechnungsvorgang war in weniger als einer Sekunde abgeschlossen.

- ABU: 5:17 Minuten (1:58 Min Schaltbild einlesen, <1s Processing, 3:19 Resultat zurückschreiben). Dabei hängt die Zeit des Einlesens und des Zurückschreibens von der Größe des Schaltbildes ab, und nicht vom Umfang der Änderungen.

Die manuelle Bearbeitung der gleichen Aufgabe durch einen geübten Bearbeiter, der sämtliche Bearbeitungsschritte ohne Nachdenken durchführen könnte, dauerte 7:50 Min. Nicht eingerechnet wurde hier der Zeitaufwand für einen automatischen Prüflauf (Design Rule Check), der durchgeführt werden muss, um Irrtümer bei der manuellen Pinzuweisung ausschließen zu können. Im konkreten Beispielsfall schlugen hier noch einmal 1:15 Minuten für die Ausführung des Design Rule Checks zu Buche, dazu kamen noch weitere 3:00 Minuten für die Einarbeitung ins Schaltbild.

- Manuelle Schaltbildbearbeitung: 7:50 Minuten, excl. DRC Ausführung ohne Bearbeitung (1:15 Minuten), excl. notwendiger Einarbeitung ins Schaltbild (3 Minuten)

Deutliche Verkürzung der PCB-Entwicklungszeit

Das Ergebnis fällt also bereits bei einem sehr einfachen Anwendungsfall, auch ohne Berücksichtigung des Design Rule Check, der im Fall der manuellen Schaltbildbearbeitung zwingend notwendig ist, eindeutig zugunsten von ABU aus.

Bei komplexeren Use Cases jedoch bleibt die Laufzeit für den Automatic Block Update relativ konstant, wohingegen die Dauer bei der manuellen Schaltbildbearbeitung mehr als linear anwachsen wird.

Zu bemerken ist dabei, dass die Zeit des Einlesens und des Zurückschreibens im Wesentlichen von der Größe des Schaltbildes abhängt, und nicht vom Umfang der Änderungen im eigentlichen Block Update.

Neues Live Webinar

Wenn Sie sich für die Funktionalität des Automatic Block Update für CR-8000 interessieren, sollten Sie unbedingt unser Webinar am 14. Oktober ansehen. Marcel Voges, Customer Support Engineer, zeigt Ihnen dort alle Details und beantwortet gerne Ihre Fragen.

- Webinare

- Software Testversionen

CR-8000 ist eine Suite von Anwendungen, die den gesamten Zyklus des PCB-Engineerings abdecken: von der Architekturplanung über das Engineering auf Systemebene und die Optimierung bis hin zur physikalischen Implementierung in 2D/3D und der Datenaufbereitung für die Fertigung. CR-8000 umfasst die Module Design Force und Design Gateway sowie weitere spezifische Module.