- Blog

After a lengthy quiet period, the hardware design process is suddenly experiencing numerous changes in the form of design discipline convergence and process extension. The widely used 2D single board PCB detailed design process is being replaced by a 3D multi-board and multi-discipline one.

- Blog

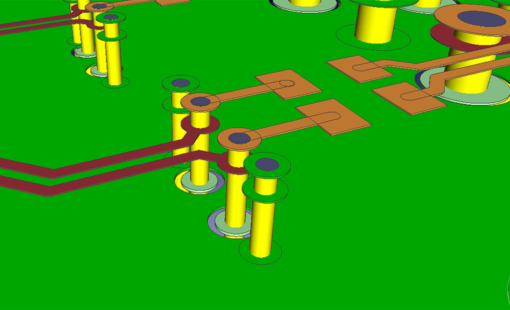

The PCB design team at Renishaw work with flex PCBs and flexi-rigid boards that require detailed signal integrity analysis. To achieve the most accurate results they are working with Zuken’s electronic PCB design software to visualize boards in 3D using imported MCAD data. This also ensures that sure high-speed digital signals can be transmitted with minimal distortion.

- Blog

I recently talked on predictive failure analysis at the PTC LiveWorx 2017 conference. There was a lot of audience interest, so I thought I’d share some of the things I discussed. This is the second of two posts on this subject.

- Blog

I recently talked on predictive failure analysis at the PTC LiveWorx 2017 conference. There was a lot of audience interest, so I thought I’d share some of the things I discussed.

- Blog

No more distractions, please! 45% of our time is already spent on admin. If you’re the average engineer, that is.

- Blog

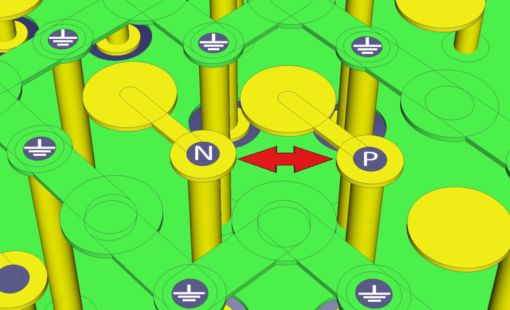

With key functionality in many cases commoditized, the success or failure of wearables is increasingly determined in the early stages of the PCB and mechanical integration process where requirements are translated into practical design decisions such as how functions are mapped to PCBs and PCBs are integrated into the enclosure.

- Blog

In the final installment of this blog series, you can learn how to use build-up layers and premium FPGAs to deal with the signal integrity challenges arising from high-speed signals in a 3D design capture world.

- Blog

This is the second in my series of blog posts looking at the challenge of maintaining PCB signal integrity with now-common ultra-high speeds and growing adoption of PCB design environments to design in true 3-D. Today I focus on vias and the use of return vias to overcome the issues highlighted in Part 1.

- Blog

Ultra-high signal speeds demand detailed consideration of the third dimension in PCB design, including via structures and layer stacks. Today I’m going to focus on the challenge. In my two subsequent posts I’ll be reviewing what PCB designers can do to meet that challenge.

- Blog

In my previous post in this series about effectively reusing design modules to increase product quality and decease development time, I challenged you to think about how well you’re making use of existing design modules and why getting better at this could be a competitive differentiator.

- Blog

In this two part series of blog posts, I’m going to be looking at reuse with modular design in PCB development, and how you can streamline your methodology to reduce design time, reduce design errors and increase product quality.

- Blog

As companies benefit from the global supply chain in terms of lower production costs and faster turnaround times, they are also exposing their intellectual property to third parties, including PCB design data.

- Blog

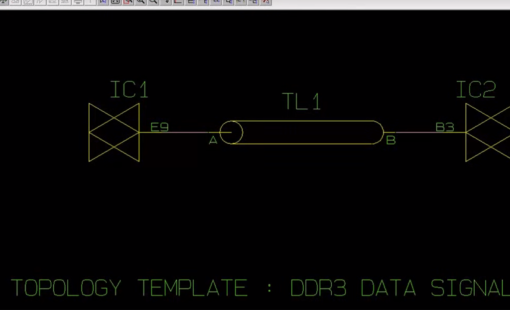

As Zuken technology partners, we are often asked about how best to set PCB constraints for double-data-rate (DDR) memory, and how to route to those constraints. This question arose recently when we were asked to create a common style of DDR3 design for training, and we tried mining the web for detailed information on PCB constraints. There had to be something out there, we thought.

- Blog

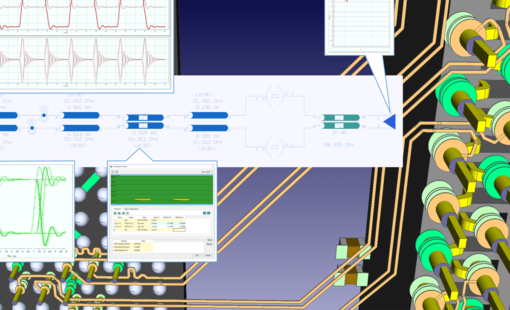

Previously I introduced you to the concept of S-Parameters, and now I’m going to explain a bit more about measuring them and simulating with S-Parameter models.

- Blog

I’d like to explain to you in straightforward terms what S-Parameters are and why they’re so useful. When I say “straightforward”, I mean that in a technical sense, but this is a specialised area. If you’re not designing high-speed PCBs, or you don’t know much about signal integrity, you might want to tune out now.