Bei dem Design von DDR4 Schnittstellen (Double Data Rate 4) auf Layoutebene geht es wie bei vielen anderen High-Speed Anwendungen auch um das Problem den Zugriff auf große Datenmengen mit der höchstmöglichen Geschwindigkeit zu ermöglichen. DDR-Technologie wurde 1998 in der Nachfolge von synchronen SDRAMs eingeführt. DDR Speicher nutzen zur Datenübertragung sowohl die fallende als auch die steigende Flanke des Taktsignals an den Prozessor und erzielt auf diese Weise pro Zyklus die doppelte Übertragungsrate (daher ‚double data rate’).

Diese Technik erlebte seitdem eine kontinuierliche Weiterentwicklung bis hin zur 5. Generation im Jahre 2021, und DDR6 ist für 2024 geplant. Obwohl sich die Anwendung bereits in Richtung DDR5 entwickelt, ist DDR4 (bzw. die Low-Power-Version LPDDR4) in der aktuellen Technologielandschaft eine entscheidende Komponente für effiziente und leistungsstarke Speichersubsysteme in einer Vielzahl von Anwendungen.

DDR3 vs. DDR4 – was ist der Unterschied?

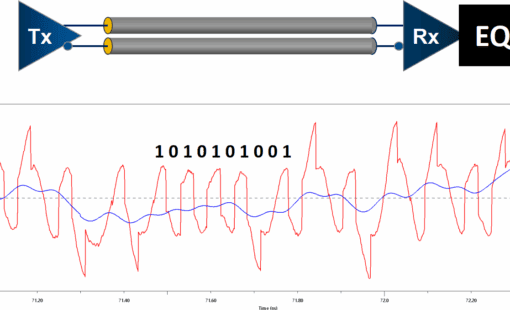

Auch wenn sich die Architekturkonzepte im Vergleich zu früheren Generationen nicht grundlegend geändert haben, so ist die Entwicklung von PCBs mit DDR4-Systemen etwas anspruchsvoller. Die Datenübertragungsrate ist in DDR4 durch die Verbesserung der Pre-Fetch Technologie und die neue DBI-Technologie (Data Bus Inversion) jetzt doppelt so hoch wie in DDR3, was eine genauere Implementation der Längenanpassung der einzelnen Signalgruppen (→ Skew-Regeln) und die Einhaltung der Signalintegritätsbedingungen erfordert.

Das Pre-Fetch in DDR-Systemen verbessert die Effizienz des Speicherzugriffs, indem ein größerer Datenblock (Pre-Fetch-Puffer oder auch als Burst bezeichnet) abgerufen wird, bevor er spezifisch angefordert wird. Dieser quasi „vorausschauende“ Ansatz trägt zur Verbesserung der Speicherlatenz bei, indem der Speichercontroller Operationen überlappt, ausführt und den nächsten Datensatz in den Pre-Fetch-Puffer holt, während die aktuellen Daten an die CPU übertragen werden (Quelle: Wikipedia).

Bei den neu hinzugekommenen DBI-Signalen überwacht der Controller die Anzahl der 0en und 1en in jedem Byte der ausgehenden Informationen. Normalerweise repräsentiert eine 1 einen hohen Pegel und eine 0 einen niedrigen Pegel. Wenn es mehr 0en als 1en gibt, invertiert der Controller das Datenwort und sendet ein Signal aus, das darauf hinweist, dass die Daten invertiert sind. Dies minimiert die Last auf dem Datenbus, und führt zu einer Reduzierung des Energiebedarfs (fast) um den Faktor zwei. Es ist wichtig zu beachten, dass dies für das Speicher-Interface gilt daher keine Eigenschaft des gesamten Boards darstellt

Routing von DDR4 Systemen

DDR4 ermöglicht eine höhere Speicherdichte und die Speichermodule haben je nach Package eine größere Anzahl an IC-Balls bei geringerem Ball-Abstand ( BGA-Pitch) was Herausforderungen in Bezug auf Routing mit sich bringt. Die Bewältigung dieser Anforderungen erfordert fortschrittliche PCB-Designtechniken, um folgende grundlegende Regeln einzuhalten:

- Die Signale eines Datenbytes- sollten möglichst auf der gleichen Lage (bzw. den gleichen Lagenpaaren) geroutet werden, bevorzugt als Stripline-Konfiguration (→Innenlagen).

- Adress-/Befehls-/Control- und Clocksignale (Control und Clock differentiell) sollten auf elektrisch gleichen Lagen (Impedanz) geführt werden (bei Platzproblemen können Lagenwechsel notwendig sein, diese sollten aber nach Möglichkeit minimiert werden, hier sind üblicherweise Constraints für die maximale Anzahl von Lagenwechseln üblich).

- Rückstrompfad-Vorgaben der IC-Hersteller (→Referenz-Planes) sind zwingend zu beachten.

- Nicht alle Speichercontroller unterstützen T/Y Topologien, dann ist bei Nutzung von mehr als einem Speicher eine Fly-By Topologie (→Daisy Chain) zwingend, dies erfordert mehr Sorgfalt im Hinblick auf Signal-Integrity (Reflektionen im Bus).

- Bei Verwendung von Daisy-Chain-Routing sollte am Controller begonnen werden (Chip 0) und dann durch bis zu „Chip n“ in der Reihenfolge der Byte-Lanes.

Darüber reduziert sich die Betriebsspannung von DDR4 auf 1,2 Volt im Vergleich zu 1,5 Volt bei DDR3. Diese Spannungsabsenkung trägt wesentlich zur Verbesserung der Energieeffizienz bei, einem entscheidenden Faktor bei vielen Elektroniksystemen, die darauf abzielt, den Stromverbrauch zu senken und so z.B. die Batterielebensdauer in tragbaren Geräten zu verlängern. Der Umstieg auf niedrigere Spannungspegel bringt jedoch auch Herausforderungen in Bezug auf die Signalintegrität und Versorgungssystem Stabilität (Power-Integrity) mit sich. Wenn die Spannung absinkt, werden die Signale anfälliger für Rauschen, Signal-Dämpfung und für andere Faktoren, die ihre Pegel und die Qualität beeinträchtigen können.

Weitere Überlegungen zum DDR4-Design

Die Aufrechterhaltung der Signal- und Versorgungssystemintegrität wird so zu einem kritischen Aspekt des DDR4-Designs und erfordert eine sorgfältige Berücksichtigung von Faktoren wie Impedanzanpassung, Signalabschluss und fortschrittliche PCB-Layout-Techniken, um eine zuverlässige Kommunikation und optimale Leistung bei reduzierten Spannungspegeln zu gewährleisten. Der Kompromiss zwischen Energieeffizienz und Signalintegrität unterstreicht die Komplexität und den sorgfältigen Balanceakt, der mit dem Design von DDR4-Systemen verbunden ist.

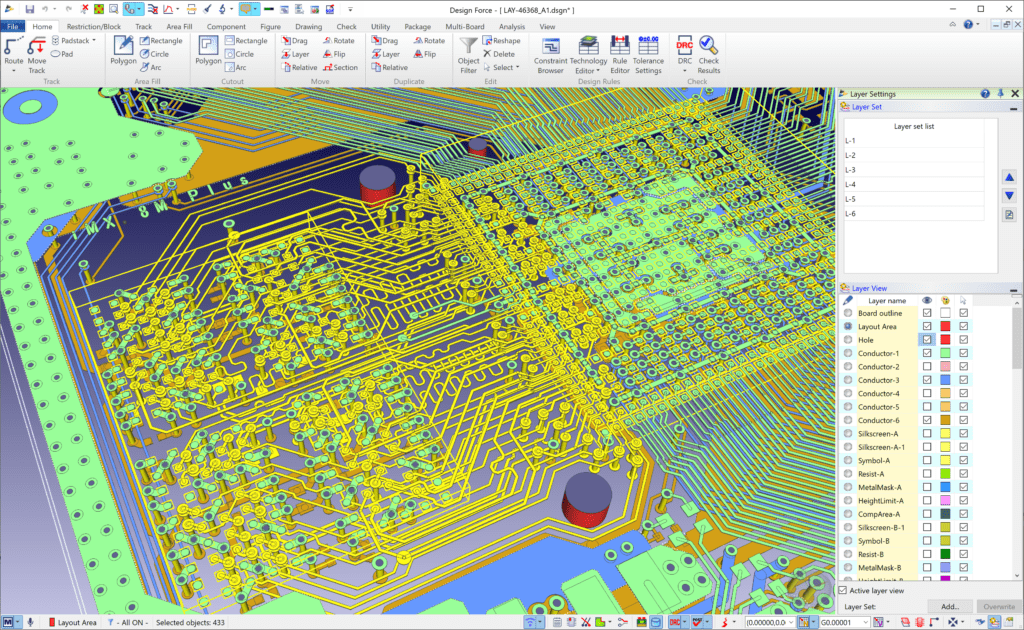

Abschließend ist zu sagen, dass DDR4-Design kein „Hexenwerk“ darstellt und nichts mit Magie zu tun hat – es erfordert aber Fleiß und Sorgfalt in der Entwicklung. Was Sie alles beachten sollten, erfahren Sie in meinem on-demand Webinar. Dort erkläre ich die Vorgehensweise bei der Implementierung von DDR4 Speicherschnittstellen mit CR-8000 von der Konzeptionsphase bis zur physischen Platzierung und Entflechtung sowie der Validierung für Signal Integrity und Power Integrity.

Weitere Webinare zum Thema

- Webinare

Dieser Vortrag ist keine Einführung in die DDR4-Technologie, sondern zeigt die Vorgehensweise bei der Implementierung von DDR4-Speicherschnittstellen mit Zuken CR-8000 von der Konzeptionsphase bis zur physischen Platzierung und Verlegung sowie der Validierung für SI und PI.

- Webinare

Der Trend zu Anwendungen mit geringerem Stromverbrauch stellt Leiterplattendesigner vor neue Herausforderungen. Die engen Toleranzen für Timing und Spannung erfordern einen ganzheitlichen Entwurfsansatz, der High Speed Constraining und integrierte Analyseschritte zur Einhaltung der verschiedenen Entwurfsregeln verbindet.