EMV Probleme sind in der Leiterplatten-Konstruktionspraxis oft dafür verantwortlich, dass Re-Design-Zyklen notwendig werden. Aufgrund von immer kürzeren Innovationszyklen von z.B. Mobiltelefonen oder IoT Applikationen wie Fitness-Trackern und vielen weiteren Elektronikprodukten, sind diese zeitintensiven Re-Design-Zyklen unbedingt zu vermeiden.

Elektromagnetische Verträglichkeit (EMV) ist das Teilgebiet der Elektrotechnik und der Physik, das sich mit der unbeabsichtigten Erzeugung, Ausbreitung und dem Empfang von elektromagnetischen Wellen (im E und H-Feld) befasst, die dann in elektronischen Geräten unerwünschte Wirkungen wie funktionale Störungen, Fehlfunktionen oder sogar physikalische Schäden verursachen können.

Dabei sind zwei grundlegende Aspekte zu berücksichtigen. Das Emissionsverhalten bezieht sich auf die unerwünschte Erzeugung von elektromagnetischer Energie durch eine Quelle und deren Übertragung auf die Senken und auf die Gegenmaßnahmen, die ergriffen werden sollten, um diese Abstrahlung zu reduzieren. Die jeweilige Störanfälligkeit bezieht sich auf den Betrieb von elektrischen/elektronischen Geräten (oder Komponenten), die “Opfer” von solchen unbeabsichtigten elektromagnetischen Störungen werden.

Grundsätzlich geht es also bei der EMV um die Fähigkeit elektronischer Systeme, in einer gemeinsamen elektromagnetischen Umgebung zu funktionieren, ohne erstens von anderen Systemen gestört zu werden und zweitens andere Systeme zu stören.

Potentielle Störquellen verstehen

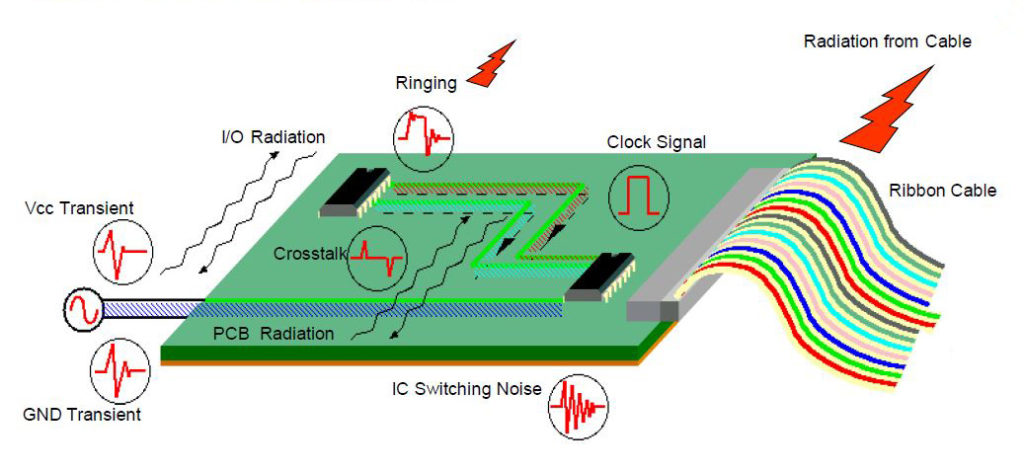

Auf einer Leiterplatte gibt es nun aber verschiedene potentielle Stör-Quellen, die eine Vielzahl von potentiellen Effekten aus den folgenden Kategorien hervorrufen können:

- Signal und Power Integrity (leitungsgebundene Störungen)

- Abgestrahlte Emission

- Störfestigkeit gegenüber abgestrahlter und leitungsgebundener Störung

- ESD

Oft unbeachtet bildet zum Beispiel das Flachbandkabel an einem Leiterplatten-Stecker physikalisch den Arm eines Dipols und bildet damit eine Parasitäre Antenne. Im Schaltvorgang der aktiven Bauteile auftretende Strom- und Spannungsspitzen in der Energieversorgung können dann zu einer Anregung dieser Antenne und einer erhöhten Abstrahlung führen. Auch sind in der Digitaltechnik Signale in der Theorie ideale Rechtecke, die aber in der Realität so nicht existieren, sondern die Signale sind mehr oder weniger verzerrt und gestört. Die dabei anfallenden Spannungsspitzen der Relflexionen und Übersprecheffekte (Crosstalk) wirken sich ebenfalls negativ auf das EMV-Verhalten aus.

EMV-gerechtes Leiterplattendesign in die Produktentwicklung integrieren

EMV-gerechtes Leiterplattendesign ist entscheidend für den Erfolg eines Produkts. Nur unter Einhaltung der EMV-Vorschriften des jeweiligen Zielmarktes oder der Applikation (Beispiel: Medizintechnik, Automotive) können Produkte überhaupt erst zugelassen werden. Oft werden Probleme jedoch erst in der Testphase von Prototypen aufgedeckt, was neben fehlendem Know-How auch an fehlender Integration von EMV-Verifikationsschritten in den Designprozess liegt.

Um EMV im Designprozess unter Kontrolle zu bringen und Probleme früher zu erkennen, gibt es verschiedene Möglichkeiten. Die erste Option ist sollte die konsequente Definition und Verwendung von Design-Constraint-Prozessen, gerade für Signal- und Power-Integrity I&PI Aspekte, im Entwurfsprozess sein.

Toolgestützte EMV-Design Reviews

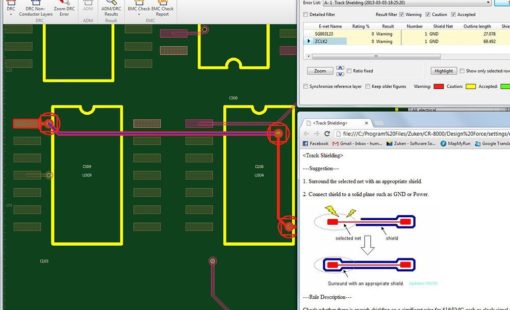

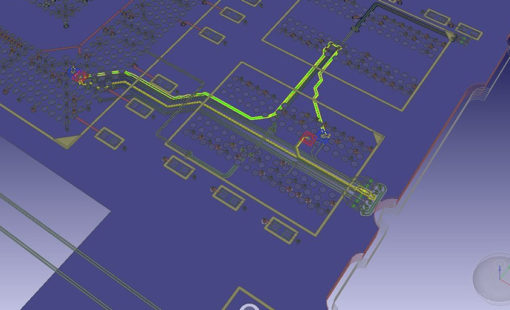

Des Weiteren können toolgestützte EMV-Design Reviews eingeführt etabliert werden, um sicherzustellen, dass entsprechende EMV Richtlinien eingehalten werden. In CR-8000 Design Force gibt es dafür EMV-Design Rule Checks, bei denen man bestimmte Regeln an oder abwählen und auch gewichten kann. Der Schaltungsentwickler kann bereits bei der Schaltplanentwicklung EMV-relevante Signale für solche Checks klassifizieren. Die der Anwendung geeigneten EMV Regeln werden dann ausgewählt und während der Entwurfsphase angewendet.

Die direkte Integration in den CAD-Prozess (2D und 3D) und die automatische Erzeugung von Berichten in der Art von DRC-Checks wie sie jedem Layouter geläufig sind erleichtern die Anwendung. Diese Berichte mit Bildern und jeweiligem Fortschrittsstatus oder Approval-Informationen können als Excel-Dokumente zwischen den Mitgliedern des Entwicklungsteams ausgetauscht werden, werden aber auch in den Designdaten hinterlegt für die gemeinsame Bearbeitung von EMV-Aspekten im Designteam.

Die im EMC-Adviser für Design Force implementierten Regeln enthalten Empfehlungen für verschiedenste Designfragen, die es auch Nicht-Experten ermöglichen, Probleme mit Signalintegrität, Power Integrity und der Elektromagnetischen Verträglichkeit zu lösen und so helfen, ein fehlerfreies, EMV-gerechtes Layout zu entwickeln. Es ist keine zusätzliche Software erforderlich, um die identifizierten potentiellen EMV Probleme zu überprüfen.

Hier noch ein schnelles „EMV-Erste-Hilfe-Kit“ für PCB Designer

Für ein EMV-gerechtes Leiterplattendesign sollte man die folgenden vier Aspekte unbedingt beachten:

-

Parasitäre Antennen identifizieren und bewerten

Es sollte unbedingt erarbeitet werden, wo auf der Leiterplatte parasitäre Antennen entstehen könnten. Parasitäre Antennen sind unter anderem sich bildende elektrische oder magnetische Monopol- oder Dipol-Strukturen.

-

Rückstrompfade kennen und berücksichtigen

Elektrischer Strom fließt zwingend zu seiner Quelle zurück. Somit spielt die Visualisierung von Rückstrompfaden und Schleifen eine wichtige Rolle. Je nach Applikation fließt der Rückstrom dabei entweder den Pfad der geringsten Impedanz oder den des geringsten Widerstands. Um einen richtigen Rückstrompfad auszuwählen, sollten Leitungen möglichst nicht über Schlitze verdrahtet werden, auch nicht bei Differential-Paaren.

-

Koppel-Effekte verstehen

Koppelpfade zwischen Quelle und Senke können entweder abhängig von parasitären Spannungen- oder parasitären Strömen entstehen oder IO-bedingt sein. Ihre Ursachen sind oft nicht direkt aus dem Layout ersichtlich.

-

Resonanzen als potentielle Antennen verstehen

Fast alle elektrischen Strukturen können resonant werden. Das gilt sowohl für Einzel-Leitungen und differielle Signale, aber auch für Versorgungsstrukturen, Kabel, Gehäuse, ja selbst für Durchkontaktierungen (Vias). Die Resonanzfrequenz lässt sich glücklicherweise für viele Strukturen mit dieser Formel leicht berechnen:

fres=1/(2π√L∙C)

Allerding ist die Kenntnis der Werte für die (parasitären) Induktivitäten (L) und Kapazitäten (C) nicht ganz so leicht zu erlangen und erfordern oft komplexe Analysen. Auch lassen sich Resonanzen lassen sich nicht vollständig ausradieren. Wichtig ist den Effekt zu kennen und zu verstehen und eine Anregung – wo möglich – zu vermeiden.

Diese und weitere Tipps für ein EMV-gerechtes Leiterplattendesign finden Sie ausführlich und praxisorientiert erklärt in unserem Webinar

- Webinare

In diesem Webinar werden einige grundsätzliche leiterplatten-gebundene EMV Probleme erläutert sowie Tips zur Addressierung dieser während des Designs diskutiert, um so das Risiko EMV-bedingter Fehlfunktionen zu vermeiden.

- Products

Sind Sie auf der Suche nach einem Werkzeug, das es Ihnen ermöglicht, die EMV Anforderungen für Ihre Produkte zu erfüllen? Dann ist EMC-Adviser EX genau die richtige Lösung für Sie!

- Webinare

- Products

CR-8000 umfasst eine Suite von Anwendungen, die den gesamten Lebenszyklus des PCB Engineerings abdecken.