In der Elektronikindustrie herrscht heute ein anhaltender Trend zum Low-Power-Design und das wird sich wohl auch in näherer Zukunft kaum ändern. Angetrieben wird er unter anderem von den Anforderungen an Leistung und Speicherdichte von mobilen Geräten, bei denen eine Reduzierung des Stromverbrauchs entscheidend ist, um die Akkulaufzeit zu verlängern, ohne dabei die Bandbreite zu beeinträchtigen.

Inzwischen finden sich Low-Power Double Data Rate Speicher (LPDDR) aber auch in anderen Branchen wie z.B. der Automobilindustrie, bei der Haushaltselektronik oder der Automatisierungstechnik. Die Elektromobilität ist weltweit der Schlüssel für klimafreundliche Mobilität und Innovation, aber sie erfordert eine hohe Energieeffizienz bei allen beteiligten elektrischen und elektronischen Komponenten, die ja letztendlich alle Energie aus der Batterie benötigen.

Dieser anhaltende Technologie-Trend stellt PCB-Designer vor zum Teil komplett neue Herausforderungen, auch weil die Datenübertragungsrate von Low-Power DDR4 Speicherinterfaces mehrere Giga-Transfers pro Sekunde übersteigt und gleichzeitig Anstiegs-/Abfallzeiten und Timing Vorgaben (Setup & Hold) immer weiter schrumpfen.

Hohe Speicherdichte für kleine Formfaktoren

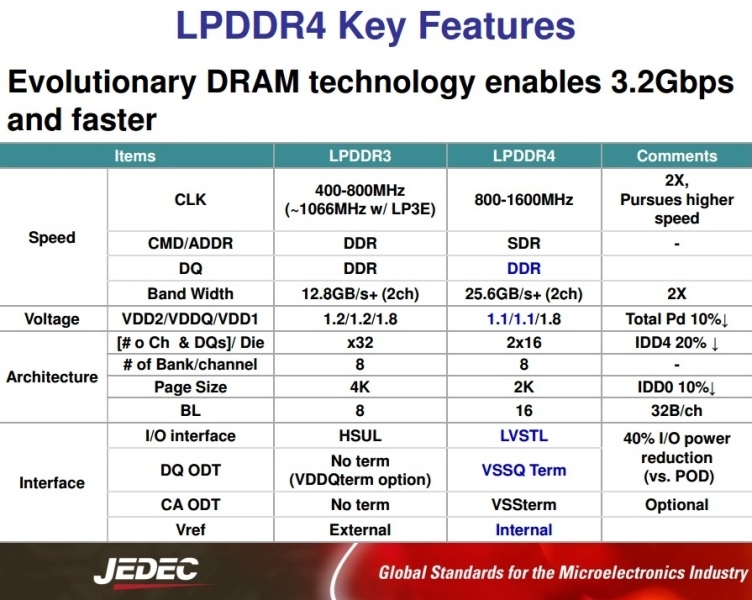

LPDDR, eine Abkürzung für Low-Power Double Data Rate, ist eine Speichertechnologie, die weniger Strom verbraucht und eigentlich besonders für Smartphones, Tablets und andere intelligente vernetzte Geräte gedacht ist. Vereinfacht ausgedrückt kann man sagen: LPDDR4 ist das mobile Äquivalent von DDR4 mit geringen Architektukturabweichungen aber der gleichen hohen Speicher-Bandbreite bei einem niedrigeren Versorgungsspannungslevel. Der Anteil dieses Typs am Markt für Speicherbausteine hat in den letzten Jahren stark zugenommen, so dass es nicht unwahrscheinlich ist, dass LPDDR4 Speicher in einer Ihrer nächsten Stücklisten auftauchen.

Was sind die Herausforderungen bei Design und Validierung?

Im Rahmen des JEDEC-Standards JESD209-4C wurden die relevanten Regeln und Einschränkungen (Constraints) für den Einsatz von LP-DDR4-Speicherbauteilen von allen Halbleiterherstellern übernommen. Dies führte zu strengeren Designregeln fürs Leiterplattenlayout im Hinblick auf Signalqualität, Timing und Güte des Stromversorgungssystems.

Hinzu kommt, dass bei vielen Applikationen die Formfaktoren immer kleiner werden (Miniaturisierung), Entwickler ringen oft um jeden Quadratmillimeter oder stellen jeden Abblockkondensator in Frage. Daher gewinnen Störeffekte wie Crosstalk oder störungsarme Abblockkonzepte immer mehr an Bedeutung.

Bei LPDDR4-Designs können zudem die ICs im Vergleich zu regulären DDR4-Designs noch umfangreicher im Hinblick auf Ihr SI-Verhalten angepasst werden, was zu vielen verschiedenen Design-Parametern führt (verschiedene On-DIE Terminierungen, Treiberstärken, Slew-Rate Control u.a.m), Diese Design-Herausforderungen sind in Bezug auf Ihre Komplexität durchaus mit dem Design von SERDES-Übertragungsstecken wie z.B. PCI-Express vergleichbar.

Herausforderungen im LPDDR4 Design meistern

Die engen Timing- und Spannungsvorgaben erfordern einen ganzheitlichen Designansatz, der High-Speed-Constraining und integrierte Analyseverfahren zur Einhaltung der verschiedenen Designregeln eng kombiniert. Besonders wichtig für den Erfolg eines LPDDR4-Designs ist eine sorgfältig durchdachte Pre-Layout-Phase. Dazu gehören Simulationen zur Ermittlung der optimalen Leiterbahnbreite (Impedanzplanung), Überlegungen zu den maximalen/minimalen Abständen zur Vermeidung von Übersprechen oder Berechnungen für Obergrenzen der Dämpfung und Laufzeitverzögerung von Durchkontaktierungen (Vias). Eine sorgfältige Planung in der Pre-Layout-Phase vereinfacht die Optimierung des Designs in Bezug auf Kosten sowie die Erzielung der maximalen Systemleistung (Speicher-Durchsatz).

In unserem on-demand Webinar „Solving Low-Power DDR4 Design Challenges“ beleuchtet Ralf Brüning, Produktmanager und Senior Consultant für High-Speed Design, das Thema von allen Seiten und erklärt die notwendigen Schritte zur Festlegung und Validierung von LPDDR4 anhand eines realen Designs, das mit CR-8000 Design Force im ersten Design-Zyklus (“First time right-Ansatz”) erfolgreich umgesetzt wurde.