Die Anordnung der verschiedenen Lagen in einer mehrlagigen Leiterplatte, gemeinhin als Lagenaufbau oder Layer-Stack-up bezeichnet, und die sorgfältige Beachtung der elektrischen Impedanz der Leiterbahnen sind entscheidende Faktoren für robuste High-Speed-Designs. Mangelhafte Entscheidungen in beiden Bereichen können zu erheblichen Leistungsproblemen führen, z. B. zu Signalverlusten, elektromagnetischen Störungen (EMI) und letztlich zu Verzögerungen und höheren Kosten aufgrund eines aufwändigen Redesigns.

Die Beherrschung des Lagenaufbaus und der Leiterbahnimpedanz ist daher für die Entwicklung zuverlässiger, leistungsstarker Leiterplatten unerlässlich. Wer die Schlüsselfaktoren kennt, die diese Designaspekte beeinflussen, und die Analyse- und Simulationsmöglichkeiten moderner Designtools nutzt, kann die Leistung und Zuverlässigkeit seiner Leiterplatten erheblich verbessern. Bevor man sich also an die eigentliche Entwicklung einer Leiterplatte macht, sollte man sich mit den wichtigsten Designparametern beschäftigen, um Stolperfallen zu vermeiden und die Gesamtleistung der Leiterplatte zu verbessern.

Die Materialauswahl ist entscheidend für die Performance – und die Kosten

FR-4 ist zwar das gängigste Leiterplattenmaterial, hat aber aufgrund seiner höheren Dielektrizitätskonstante (Dk) bei High-Speed Anwendungen seine Grenzen. Verlustarme Dielektrika wie PTFE-Laminate, keramikgefüllte Kohlenwasserstoffmaterialien oder Laminate auf Polyimidbasis bieten eine bessere elektrische Leistung bei Hochgeschwindigkeits- und Hochfrequenzanwendungen, sind aber teurer als Standard-FR-4. Außerdem sind sie weicher und erfordern daher spezielle Herstellungsmethoden, um Verformungen beim Bohren und Ätzen zu vermeiden. Kritisch sind sie auch in Bezug auf Umwelteinflüsse wie z. B. Feuchtigkeit.

Wie sieht ein gut durchdachter Lagenaufbau aus?

Die Reihenfolge, in der die Signalebenen und die Masse-/Leistungsebenen angeordnet sind, wirkt sich direkt auf die EMV-Kontrolle und das Crosstalk aus. Ein gut durchdachter Lagenaufbau ordnet schnelle und langsame Signale auf separaten Lagen an und trennt sie so voneinander. Die signalführenden Lagen sollten wiederum durch dedizierte Stromversorgungs- und Erdungsebenen ergänzt werden, um eine Abschirmung und einen stabilen Return Path zu gewährleisten. Ein typischer 4-lagiger Leiterplattenaufbau für eine ausgewogene Stromverteilung, EMI und Reduzierung des Übersprechens wäre beispielsweise Signal-Masse-Strom-Signal“. Für empfindlichere Mixed-Signal- oder Analog-Digital-Systeme bietet eine etwas teuerere ‘Signal-Ground-Ground-Power’-Konfiguration eine hervorragende EMI-Abschirmung, insbesondere für Hochgeschwindigkeitssignale.

Der Einfluss der Kupferdicke

Die Kupferdicke spielt in mehrfacher Hinsicht eine entscheidende Rolle für die Signalintegrität von Hochgeschwindigkeits-Leiterplattendesigns. Dickeres Kupfer in Hochgeschwindigkeits-Leiterplattendesigns bietet sowohl Vorteile als auch Herausforderungen für die Signalintegrität. Positiv ist, dass die Leitungsverluste durch einen geringeren Widerstand reduziert werden, was wiederum die Signalabschwächung über große Entfernungen minimiert. Außerdem wird die Signalübermittlung durch eine geringere Induktivität verbessert, wodurch Verzerrungen und Verzögerungen vermieden werden. Andererseits erschwert dickeres Kupfer die Impedanzkontrolle, da es breitere Leiterbahnen erfordert, die zu Signalreflexionen und Übersprechen führen können. Außerdem ist ein größerer Abstand zwischen den Leiterbahnen erforderlich, was das Routing in dicht gepackten Designs erschwert.

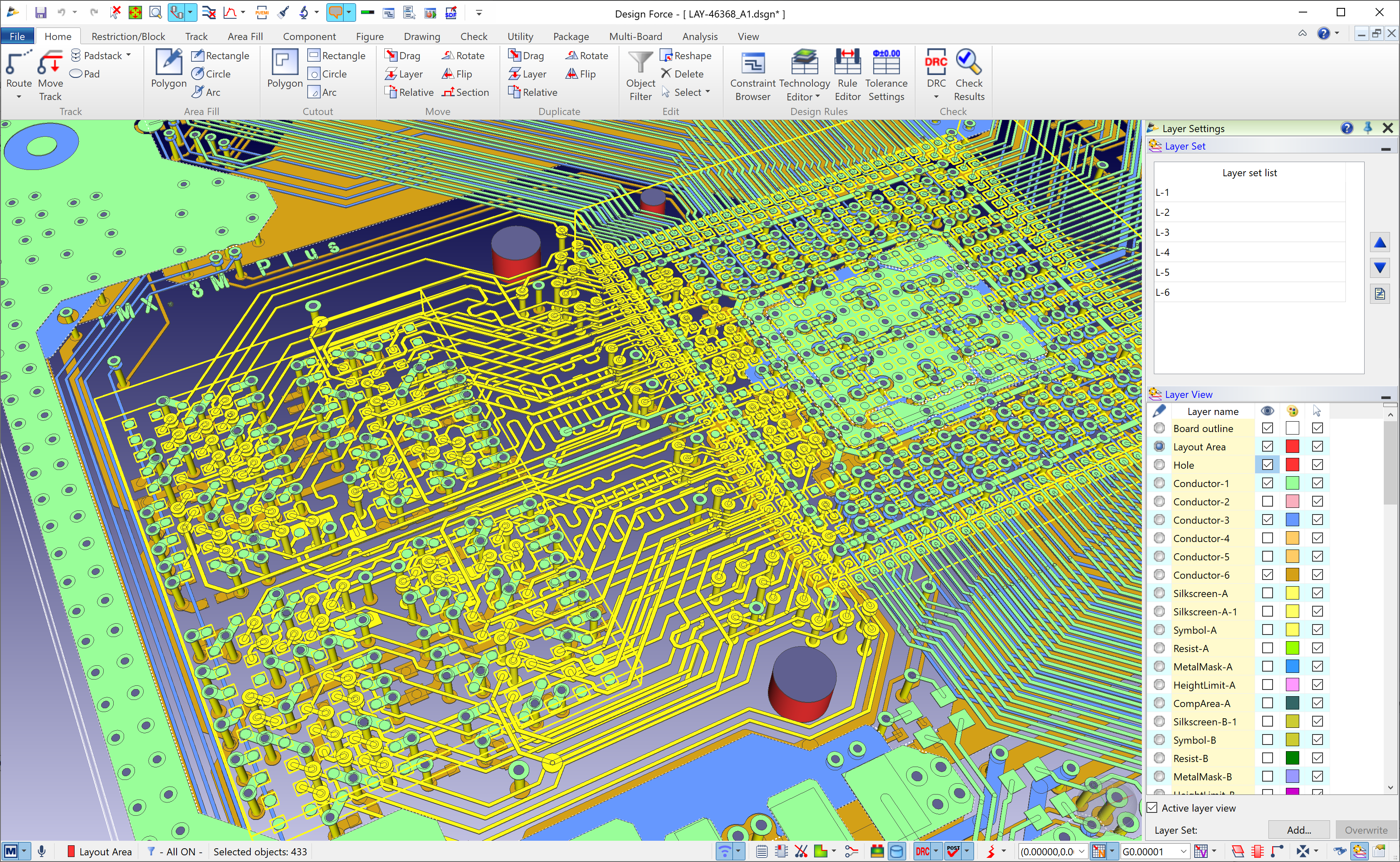

Um eine gleichmäßige Impedanz zu erreichen, ist es daher entscheidend, bereits in der Entwurfsphase die richtige Leiterbahnbreite und den richtigen Abstand zu berechnen und zu entwerfen. Moderne PCB-Design-Tools wie CR-8000 verfügen über integrierte Analysefunktionen für die Signalintegrität, mit denen die Impedanzkontrolle während des Layouts automatisch und zuverlässig durchgeführt werden kann.

Konkurrierende Anforderungen ausgleichen

Es liegt auf der Hand, dass die meisten, wenn nicht sogar alle der oben genannten Aspekte und Anforderungen ziemlich miteinander in Konflikt stehen und einen ausgewogenen Abgleich erfordern. Moderne PCB-Designsoftware wie CR-8000 kann den Designern dabei helfen, die geforderten Leistungsparameter mit integrierten Berechnungs- und Simulationstools zu erreichen.

CR-8000 bietet eine Reihe von leistungsstarken Funktionen zur Optimierung von PCB-Designs. Dazu gehört eine integrierte Signal- und Power-Integrity-Analyse, die es dem Entwickler ermöglicht, eine optimale Funktion über alle Lagen hinweg zu simulieren und sicherzustellen. Eine Stack-up-Planungsfunktion hilft bei der Festlegung der Lagenfolge und der Materialauswahl und reduziert so Interferenzen. Darüber hinaus bietet die Software eine Impedanzberechnung in Echtzeit, die während des Leiterbahnroutings automatisch die Impedanz prüft, um Konsistenz und Genauigkeit zu gewährleisten

Der Lohn der Mühe

Konstrukteure, die das Stack-up-Design und die Impedanzkontrolle beherrschen, können ihre Leiterplattenentwürfe erheblich verbessern: Sie erreichen eine bessere Performance durch verbesserte Signalintegrität mit weniger Signalverlusten, geringerem Übersprechen und geringerer elektromagnetischer Interferenz. Gleichzeitig sparen sie Zeit und Geld, indem sie kostspielige Nacharbeiten vermeiden. Dass durch optimierte Stackups die Material- und Fertigungskosten gesenkt werden, ist ein weiterer positiver Nebeneffekt.

Mehr dazu in unserem Webinar

Wenn Sie tiefer in diese Thematik eintauchen und von Expertenwissen profitieren möchten, besuchen Sie unser ausführliches Webinar (in englischer Sprache) “Challenges of Stack-up Design and Track Impedance Control“.