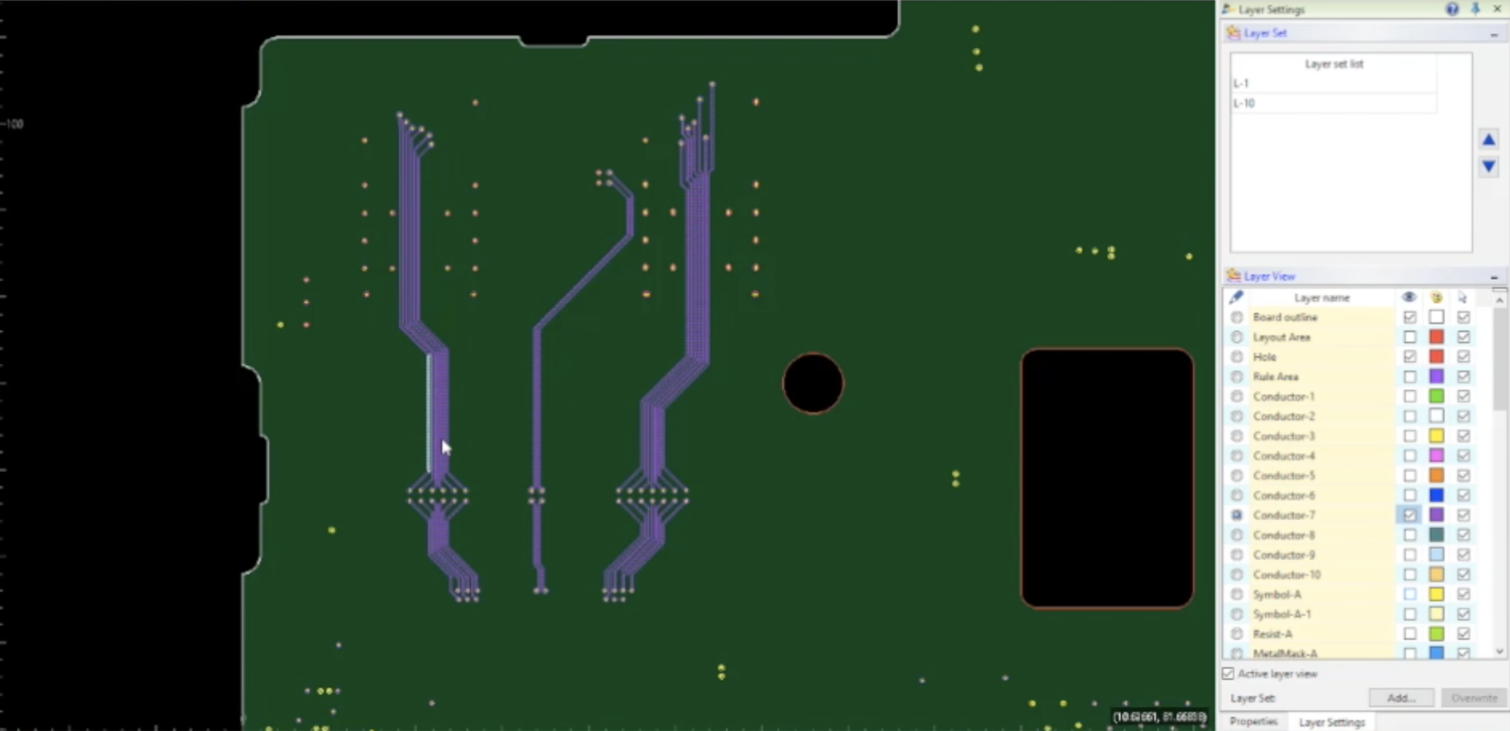

In this tech tip, we will explore how you can clear a routed trace pattern on multiple conductive layers.

In this design, the requirement is to have these traces on layer 7 to be cleared in the exact same pattern on the conductive areas which are poured on layers 6, 7 and 8.

In this completed example you will see we have these traces routed and they have been cleared on the plane on layer 7. Also, take note that the routed traces have clearances defined on layers 6 and 8.

During today’s tech tip I am going to show you how it’s done!

What we will need is an only track keepout inhibit layer defined that are associated with layers 6 and 8. To set this up I will launch the technology editor. First I will create a user-defined layer and call it InhibitTrack_Layers_6_8. Next, I will right click over the new user-defined layer and select associate with the conductive layer. In this next dialog, I will select both layers 6 and 8 and then set the Layer Type to “Only track keepout” and then select Association. Now take note that this layer is associated with layers 6 and 8.

Next, I will set the active layer to InhibitTrack_Layers_6_8 and I will select the Figure tab and select Offset.

Now I will use the Offset function located on the Figure tab of the ribbon.

In the parameters, dialog set the “Mode” to Area Fill and then set the direction to Outside. Then set the offset value to .1. Next, I will frame select the traces and the offset is generated on to InhibitTrack_Layers_6_8

So far so good!