This is the second in my series of blog posts looking at the challenge of maintaining PCB signal integrity with now-common ultra-high speeds and growing adoption of PCB design environments to design in true 3-D. Today I focus on vias and the use of return vias to overcome the issues highlighted in Part 1.

Vias explained

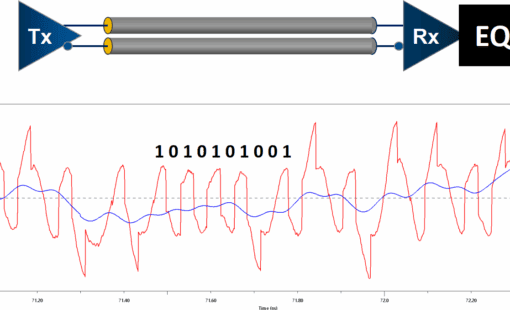

When traces that carry fast signals are long enough to become transmission lines, return paths are provided by inserting ground and power return planes. These planes pull the magnetic and electric field lines so that they are transverse to the direction the wave travels – a mode called TEM (Transverse Electric-Magnetic). Without TEM, things like characteristic impedance and unit-length delay are unpredictable and that means signal integrity is unpredictable too.

It goes without saying that the last thing we need is random signal integrity.

Really fast signals are often differential because differential signals yield better signal integrity and noise resistance than single-ended.

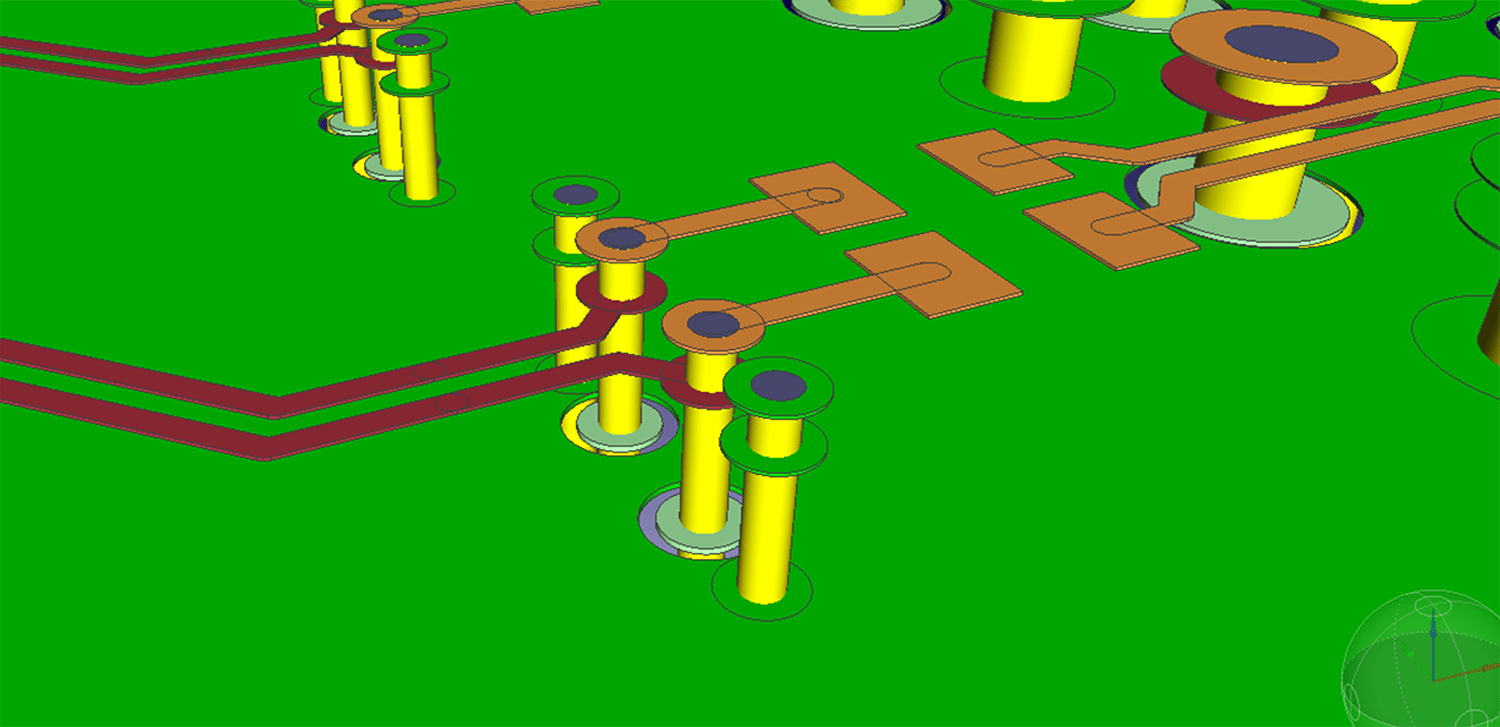

Vias connect signals in the Z dimension rather than just X and Y, but the same reasoning applies; but vias are quite complicated structures and the calculations are different.

In electronics, it doesn’t matter how a thing looks to the eye, but rather how it looks electrically.

How would we like vias to look in an ideal world?

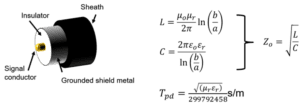

Coaxial cables are really good for carrying high-frequency signals. They’re even better than PCB traces because they’re surrounded 360 degrees by ‘ground’. Just like the PCB ground and power plane, the shield shapes the electric and magnetic fields, but impedance and delay are easier to predict and you can even use a formula.

You can’t embed true coaxial structures in PCBs without sending the cost sky-high, but you can get near enough to this ideal without too much difficulty.

How can you make vias look like pieces of coax?

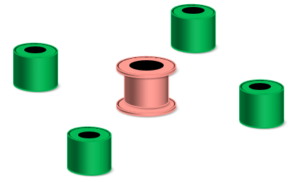

One way is to add grounded return vias at equal distances around signal vias.

An engineer did some experiments and discovered this is a good solution (details on EDN.com here).

Other solutions

Remembering the breakpoints (from Part 1) where vias become transmission lines, the other way is to get their size under those breakpoints. That’s often more economical than adding return vias and improves performance at the same time.

Here are some popular ways:

Method: Build-up layers with small, laser-drilled vias

About Method: If you need build-up anyway, then keep the really high-speed routing to the build-up layers. If you don’t need it anyway, it’s quite expensive.

Method: Backdrill to remove excess via metal from through-hole vias

About Method: Increasingly popular and benefits even slower signals, where it reduces signal delay, but it isn’t suitable for fine-line BGA fanout and other delicate structures. To minimize the number of production steps, restrict high-speed routing to a group of layers beginning with an outer layer.

Method: Use Blind and Buried Vias

About Method: This can be expensive because it adds production steps. The vias have to be drilled before the layer stack is pressed. You have to plan routing layers carefully because you can drill buried vias through hard laminate, but not through soft, pre-cured PrePreg.

It goes without saying that you can avoid all these issues by restricting routing to a single layer. There is a strong trend in this direction because the latest high-speed signals are mostly routed point-to-point.

In the next and final part, I’ll show what this looks like when you’re designing a real PCB.

Also see: