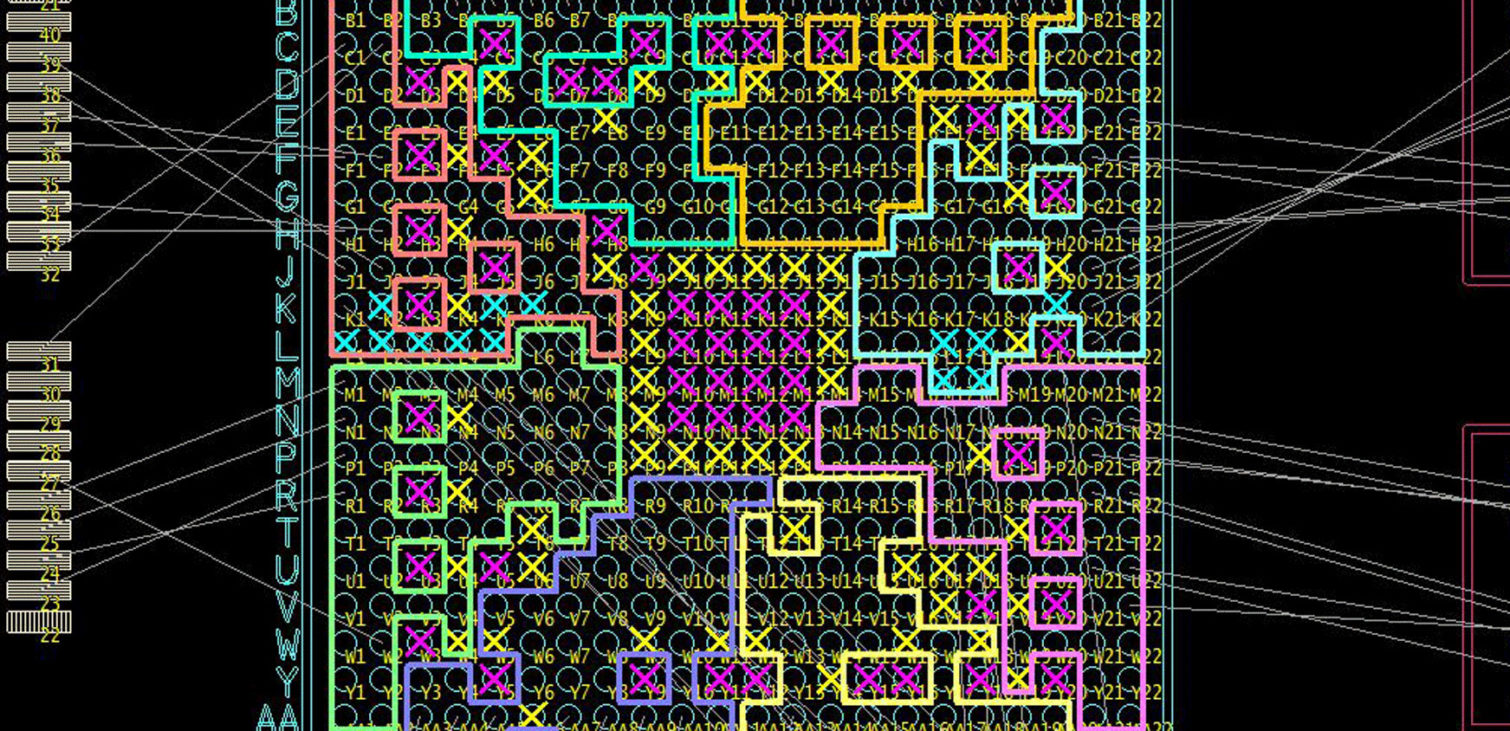

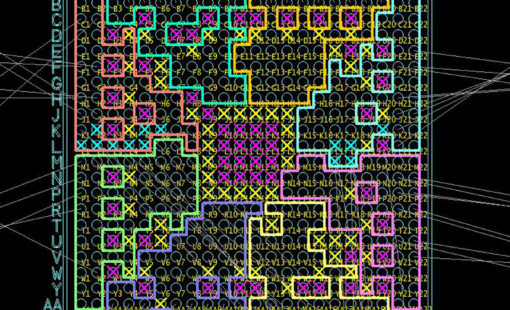

CR-8000 Graphical Pin Manager

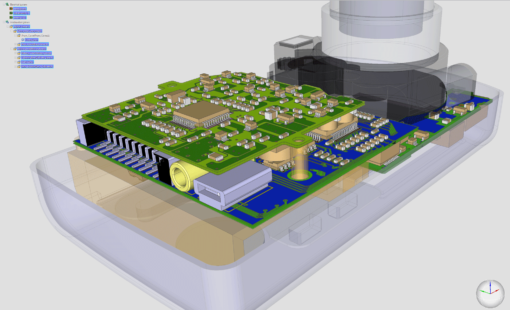

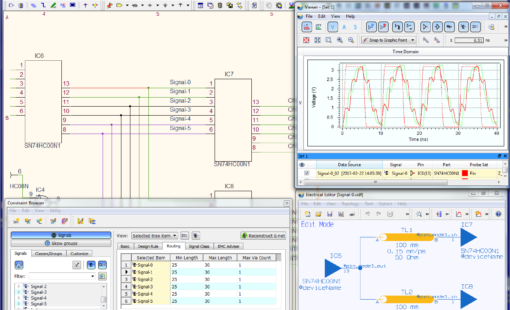

Der Graphical Pin Manager von CR-8000 bietet eine effektive FPGA/PCB Co-Design-Umgebung für die neuesten Bauelemente von Anbietern wie Xilinx, Intel, Lattice und Microsemi. Als Teil der CR-8000-Familie ermöglicht der Graphical Pin Manager Design-Teams den intelligenten Austausch von I/O- und Constraint-Informationen für FPGAs oder andere hochpolige Geräte zwischen Design Gateway und Design Force. Dadurch können programmierbare Logikdesigns parallel zum Leiterplattendesign entwickelt werden, so dass Projektliefer- und Produktionspläne ohne Verzögerung eingehalten werden können.