MultiCore-CPU-Unterstützung für effiziente Simulationen auch komplexer Fragestellungen.

Design Force SI Advance vereint eine Reihe innovativer, Funktionalitäten die Ihre Möglichkeiten im Bereich der Signalintegritätsanalyse erheblich erweitern. Mit diesem neuen Paket werden alle Aspekte der Signalintegrität von der Analyse und Optimierung von Leitungs-Impedanzen durch einen Field-Solver bis zur IBIS-AMI-Analyse von SerDes-Kanälen abgedeckt. Technische Highlights sind dabei u.a.:

MultiCore-CPU-Unterstützung für effiziente Simulationen auch komplexer Fragestellungen.

64-Bit-Rechenarchitektur für die Handhabung großer Datensätze und zur Unterstützung der Parallelverarbeitung

KI/Machine Learning unterstützte S-Parameter-Modellierung (Vector-Fitting)

Die leistungsstarken Simulationswerkzeuge von Design Force SI Advance bieten eine Vielzahl von Vorteilen, die sicherstellen, dass Ihre Elektronikprojekte erfolgreich sind und die Signalintegrität bei jedem Schritt des Designprozesses gewährleistet ist.

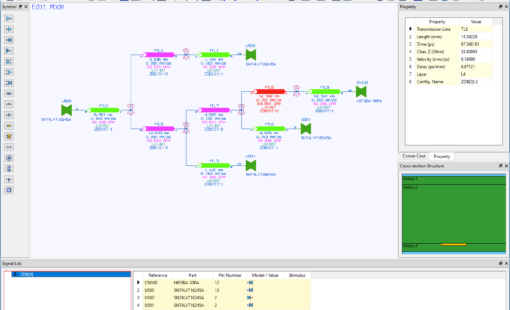

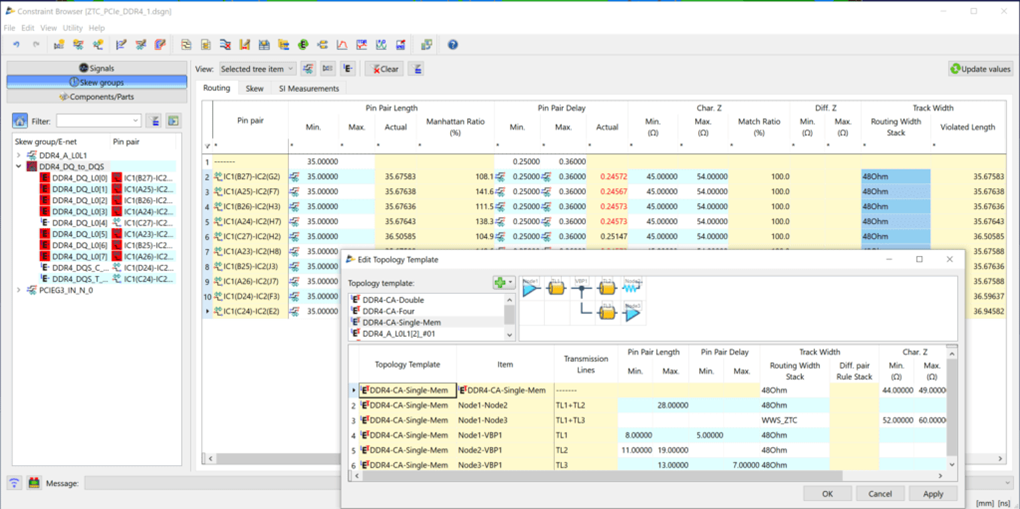

In der wichtigen Pre-Layout-Phase eines High-Speed Designs empfiehlt es sich, alle relevanten -Constraints (z.B. Impedanzvorgaben oder Laufzeitrelationen, sog. Skew) zu definieren und die Verdrahtungsreihenfolge (Topologie) kritischer Netze (z. B. für Double-Datarate Speicher) zu optimieren. Diese frühzeitige Planung legt den Grundstein für ein robustes physikalisches Design, reduziert kostspielige Fehler im weiteren Verlauf und stellt durch die Vermeidung von Iterationen sicher, dass Ihr Projekt im Zeitplan bleibt.

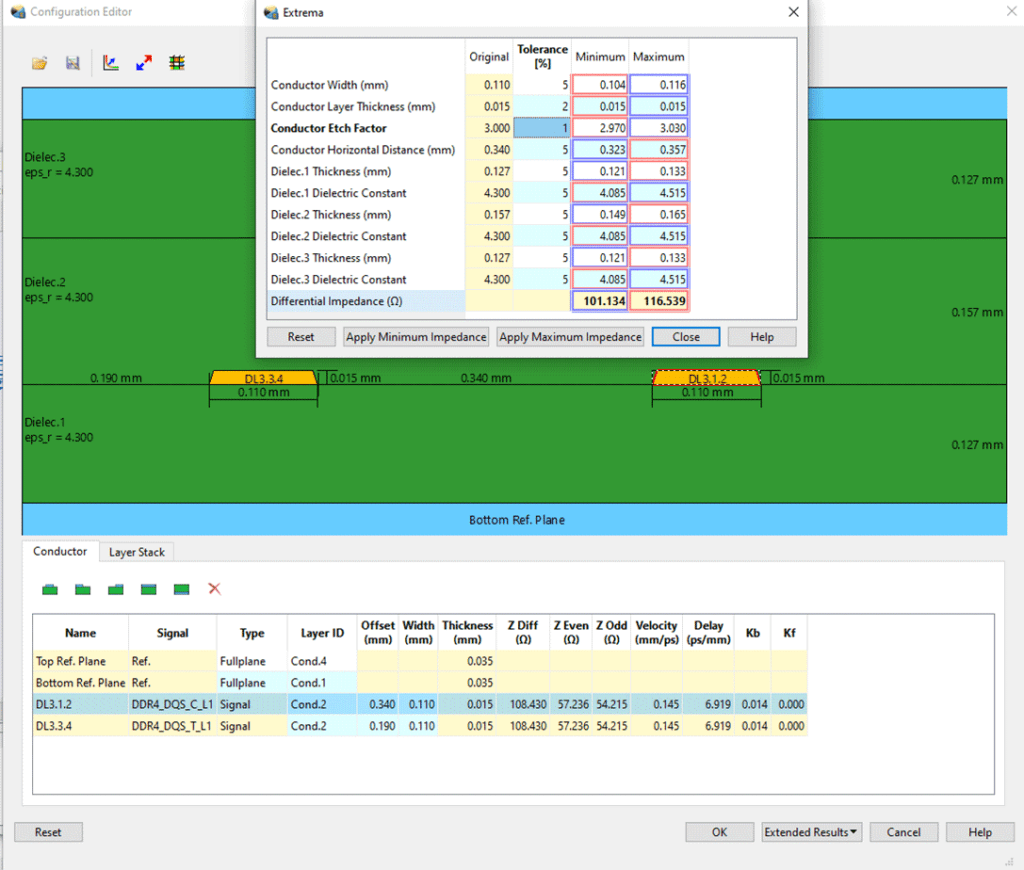

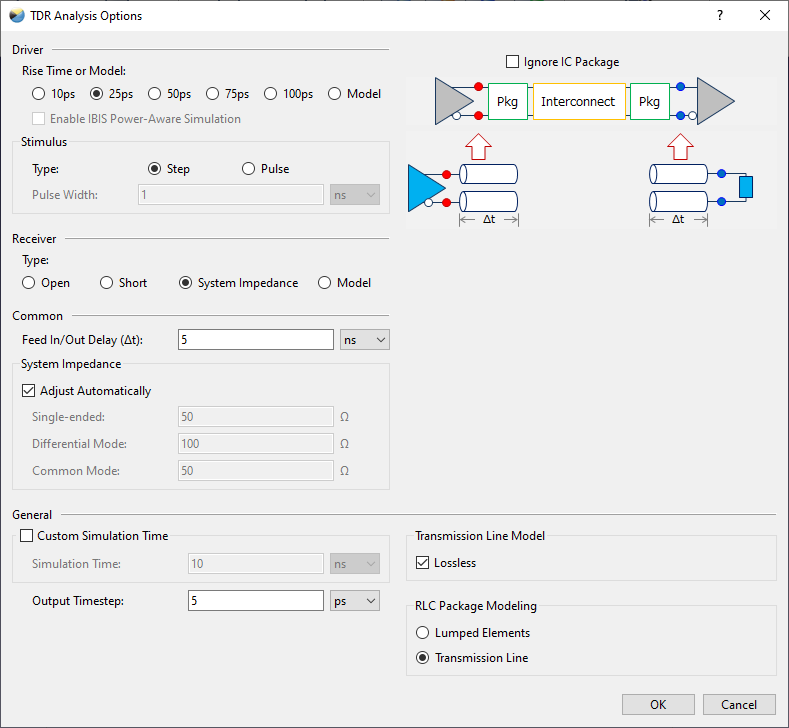

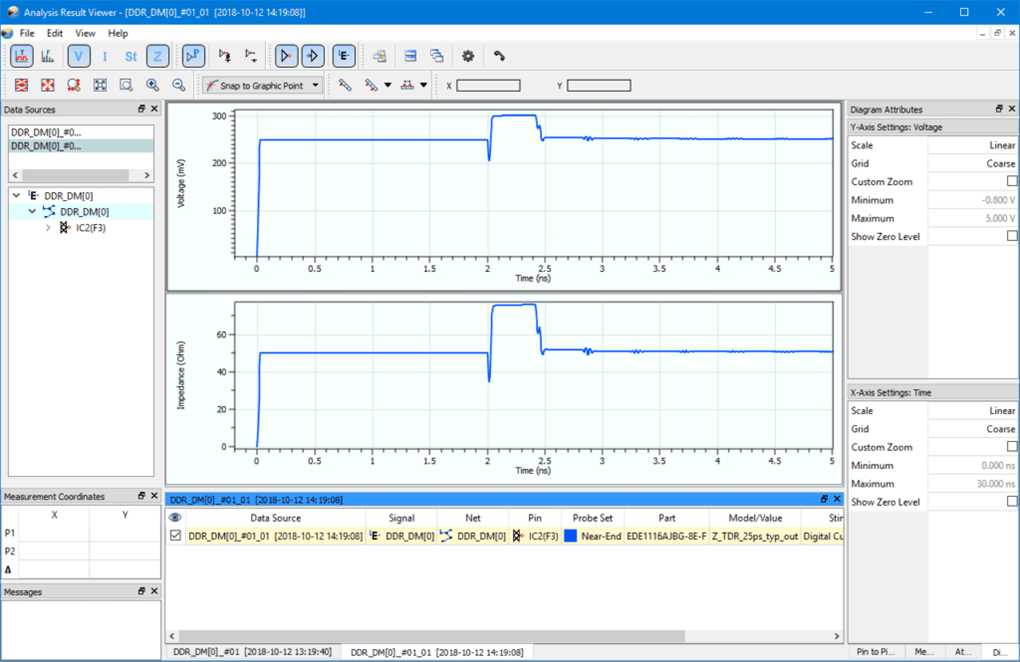

Unser integrierter Field Solver unterstützt verlustbehaftete Leitungsmodelle und versetzt Sie in die Lage, die Impedanz Ihrer Signal-Leitungen genau zu planen. Eine Toleranzanalyse und die enthaltene umfangreiche Materialdatenbank runden diese Funktionalität ab. Dieser Ansatz unterstütz das Einhalten der Vorgaben aus den Design-Regeln und maximiert die Leistungseigenschaften und stellt sicher, dass Ihre Designs auch höchsten Ansprüchen genügen.

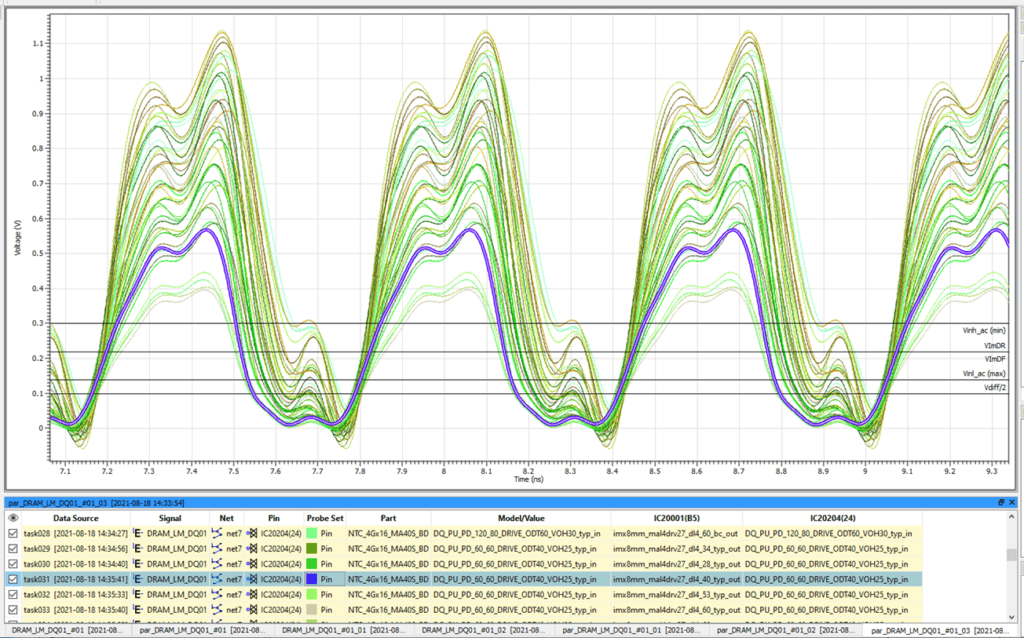

Die schnelle interaktive transiente Simulation bietet präzise Timing-, Reflexions- und Crosstalk-Analysen. Durch das schnelle Identifizieren und Beheben potenzieller Signalintegritätsprobleme sparen Sie Zeit und Ressourcen.

Die effiziente Verwaltung Ihrer Bibliothek mit einer breiten Palette von unterstützten Modellformaten (IBIS, SPICE, S-Parameter) gewährleistet den effizienten Zugriff auf die erforderlichen Informationen für eine genaue Signalintegritätsanalyse.

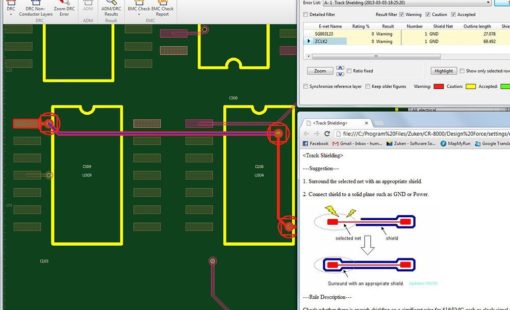

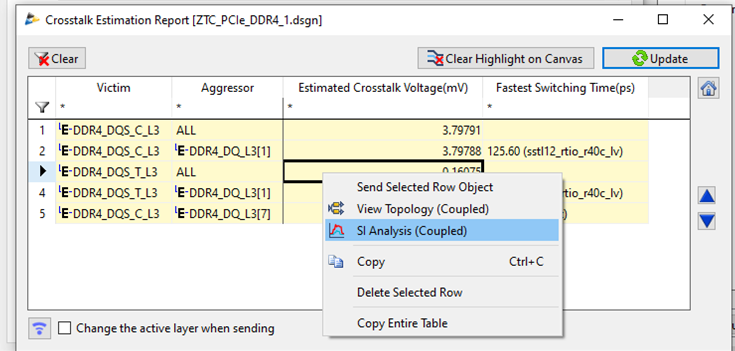

CR-8000 Design-Force ermöglicht ein schnelles Crosstalk-Screening auf der Grundlage der Field-Solver-Ergebnisse und den zugewiesenen Bauteilmodellen (siehe auch: Design-Force Crosstalk Estimation Report). Identifizierte Problembereiche können im Layout visualisiert werden. Darüber hinaus kann eine detaillierte transiente Crosstalk-Simulation durchgeführt werden, um Kopplungsprobleme proaktiv zu entschärfen und die Signalintegrität zu gewährleisten.

Die Unterstützung der Nutzung von SPICE- und S-Parameter-basierten Modellen in transienten Simulationen bietet vielseitige Modellierungsoptionen für Ihre Signalintegritätsanalyse.

By utilizing IBIS buffer models, your analysis becomes highly compatible with industry standards, ensuring seamless integration into your workflow and adherence to established norms. The support of Power-Aware IBIS models allows to include effects like SSN (Simultaneous Switching Noise) in your analysis.

Mit der Parameter-Sweep-Funktionalität können Sie Topologiestrukturen optimieren, um spezifische Anforderungen an das Schaltverhalten zu erfüllen und die optimale Leistung für verschiedenen Szenarien zu gewährleisten.

Die Verwendung von S-Parameter-Daten in der Zeitbereichssimulation erfordert die Transformation vom Frequenzbereich in den Zeitbereich, dies erfolgt durch einen Vector-Fitting Ansatz.. Die Bestimmung der optimalen Fitting-Parameter und das Erkennen der dem S-Paramter zugrunde liegenden Bauteil-Eigenschaften wird durch Machine-Learning-Technologien unterstützt, um die optimalen Anpassungsparameter für die betreffende Struktur zu ermitteln und so eine Konvergenz der Simulation sicherzustellen

Durch eine Prüfung der Ergebnisse der automatischen Timing-, Skew- und Signalintegritätsmessungen wird Ihnen ein detaillierter Einblick in das Verhalten Ihres Designs ermöglicht

Die Berücksichtigung der Auswirkung von Fertigungstoleranzen und den Materialeigenschaften ermöglicht es Ihnen, ein umfassendes Verständnis dafür zu erlangen, wie sich diese auf das Signalintegritätsverhalten auswirken. Mit diesem Wissen können Sie qualifizierte Designentscheidungen für eine erhöhte Zuverlässigkeit treffen.

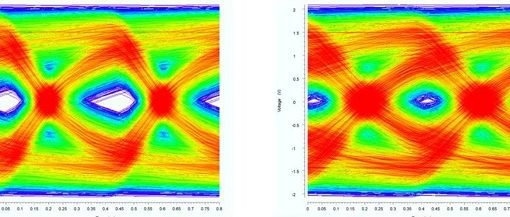

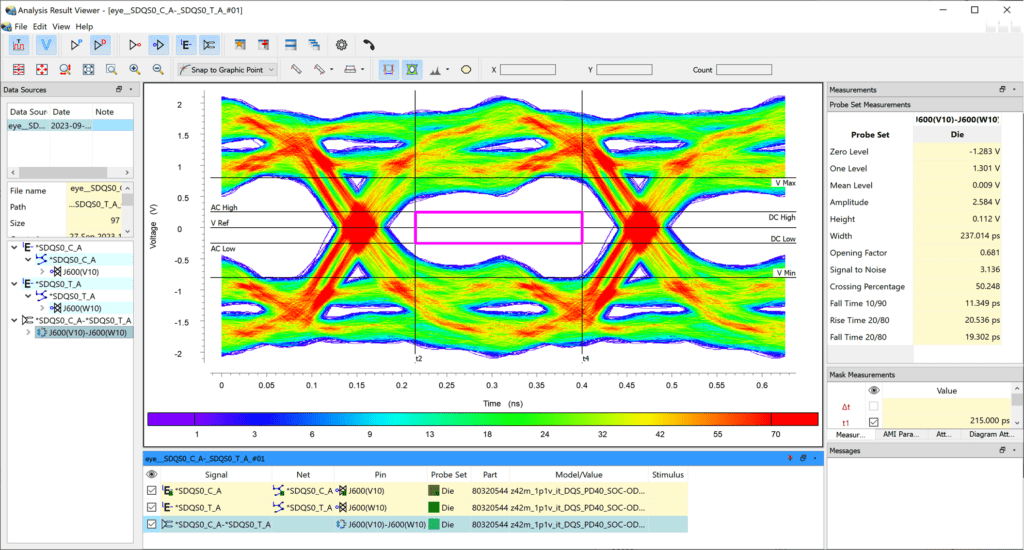

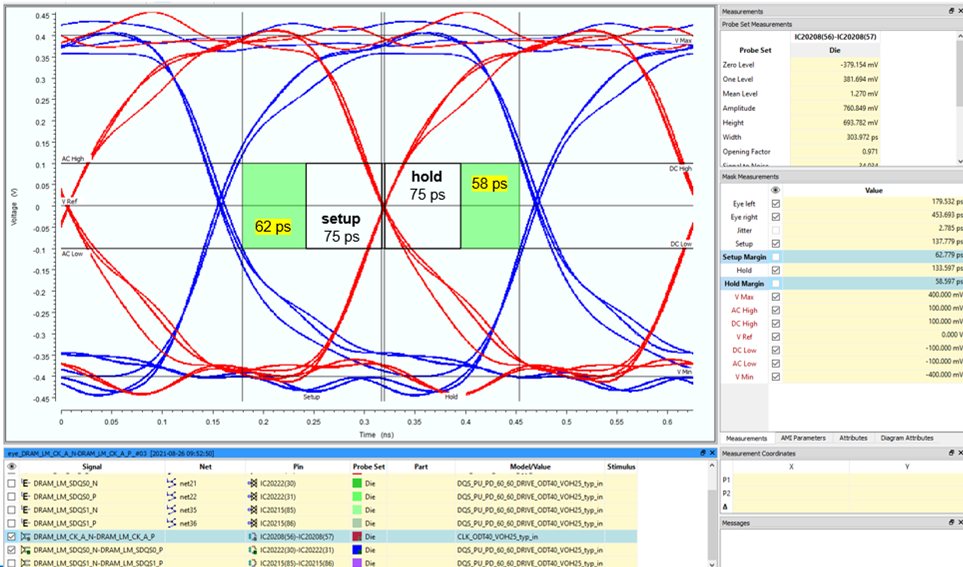

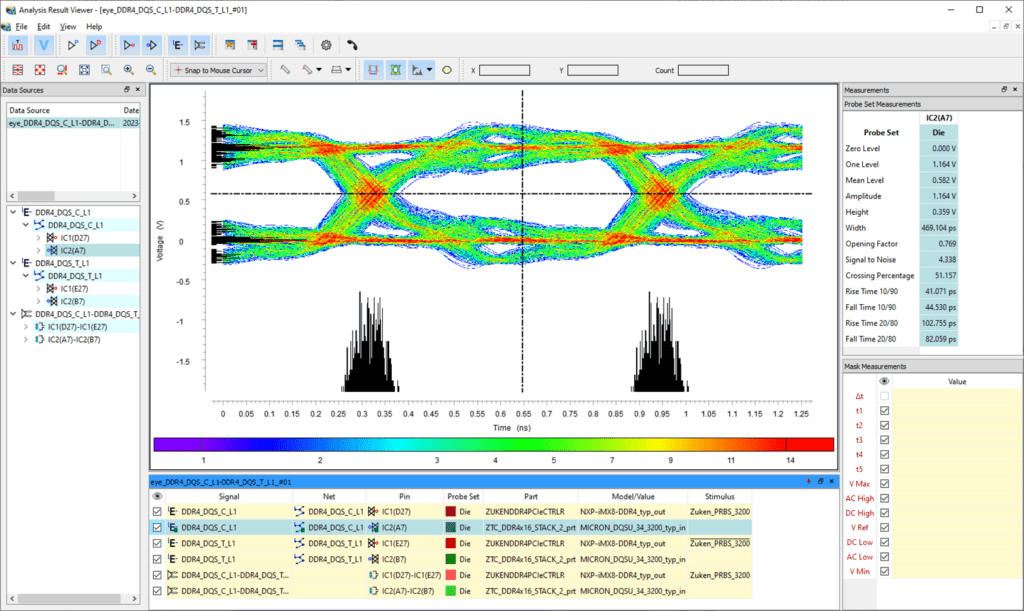

Die Visualisierung der Signalqualität mit der Eye-Pattern-Analyse (Zeitbereichssimulation) bietet ein detailliertes Bild des Verhaltens Ihres Designs sowohl für parallele Busse als auch für serielle Verbindungen.

Durch die Überprüfung des Setup- und Hold-Timings anhand von Eye-Pattern Ergebnissen und entsprechenden Complaince-Masken können Sie sicherstellen, dass Ihre Signalübertragung zuverlässig ist und auch die Timing-Anforderungen erfüllt.

Mit Hilfe von Augenmasken können Sie Signal-Standards (z.B. USB, PCI-Express, DDR) für die Signalqualität festlegen und Ihre Signale entsprechend bewerten. Dieser Prozess dient als Qualitätssicherungsschritt, der überprüft, ob Ihr Design die vordefinierten Kriterien erfüllt.

Die Visualisierung der Signalqualität mit der Eye-Pattern-Analyse (Zeitbereichssimulation) bietet ein detailliertes Bild des Verhaltens Ihres Designs sowohl für parallele Busse als auch für serielle Verbindungen.

Durch die Überprüfung des Setup- und Hold-Timings anhand von Eye-Pattern Ergebnissen und entsprechenden Complaince-Masken können Sie sicherstellen, dass Ihre Signalübertragung zuverlässig ist und auch die Timing-Anforderungen erfüllt.

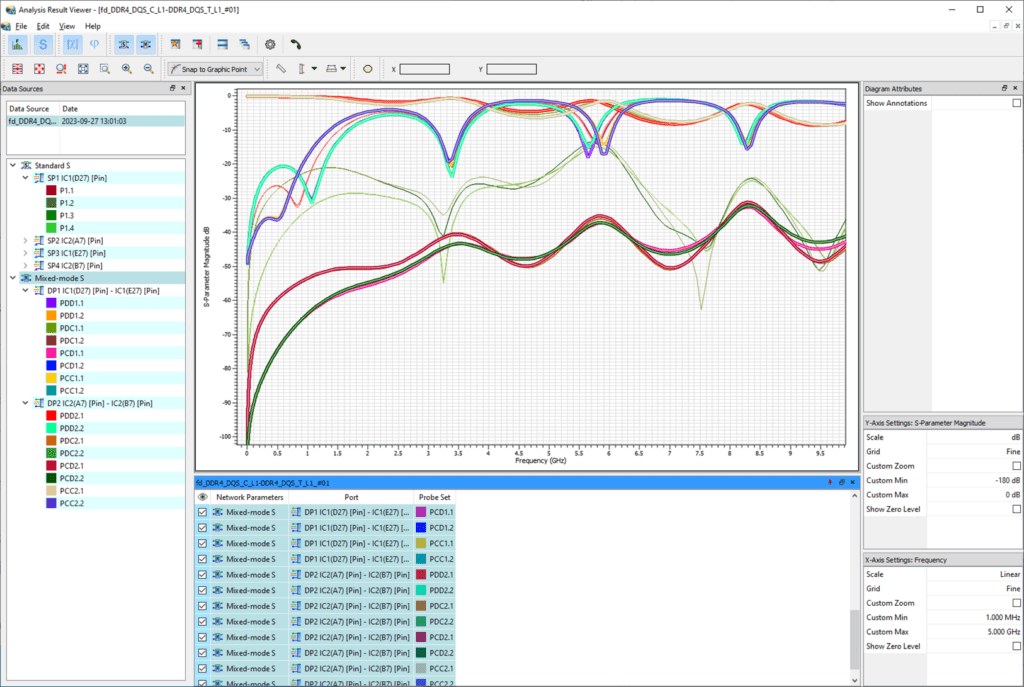

Die Berechnung von -S-Parametern für die Optimierung von Verbindungen unterstützt den Frequenzbereich bis 15 GHz.

Die Analyse von Mixed-Mode-S-Parametern erlaubt ein umfassendes Verständnis des Signalverhaltens und hilft potenzielle Probleme zu beheben.

Die Kausalität in der S-Parameter-Analyse kann bei Bedarf erzwungen werden, um die Genauigkeit und Zuverlässigkeit der Simulationsergebnisse zu gewährleisten.

Der Export von S-Parametern in das Touchstone-Standardformat ermöglicht die nahtlose Integration mit anderen Simulationswerkzeugen oder das Einlesen in Messtechnik zum Vergleich Simulation-Messung und rationalisiert die Zusammenarbeit im Team.

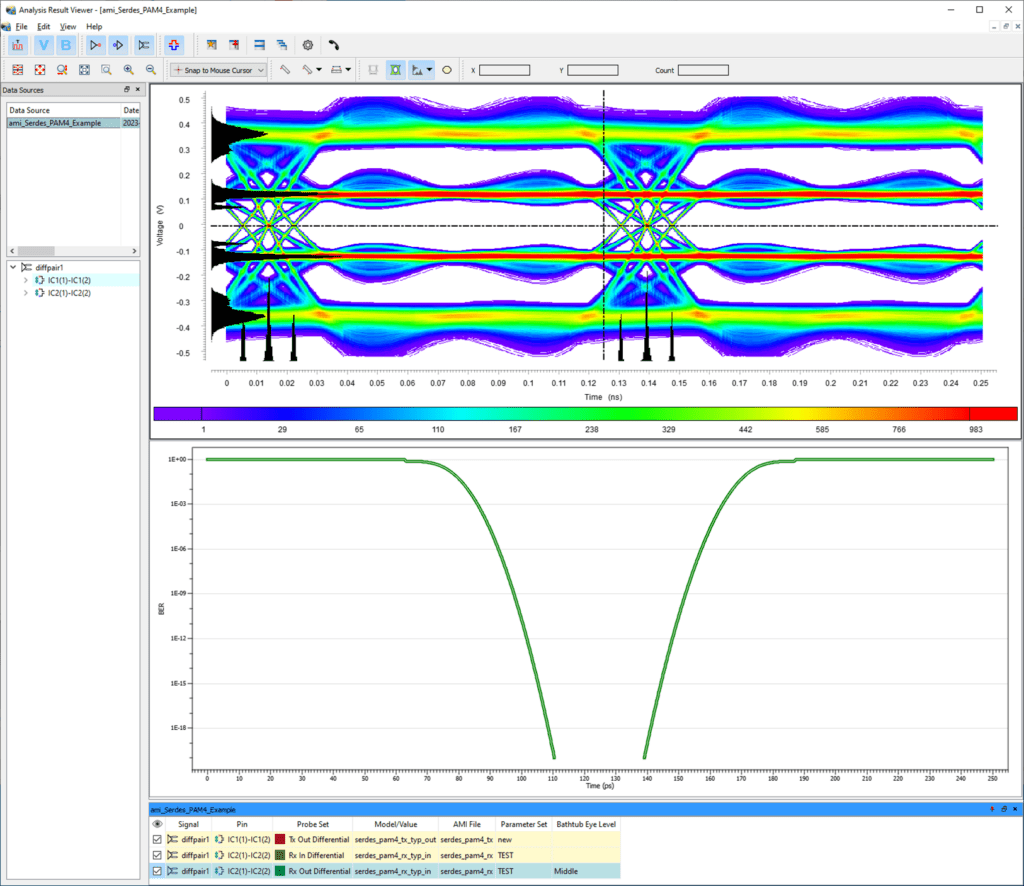

Mit Hilfe der AMI-Simulation können Gigabit-SERDES-Kanäle optimiert werden, um die Zuverlässigkeit der Datenübertragung zu gewährleisten und das Fehlerrisiko zu verringern.

Die Berechnung des Bitfehlerverhältnisses (BER) gewährleistet die Überprüfung, ob eine fehlerfreie Kommunikation im Kanal gewährleistet ist und ist ein Maß für eine zuverlässige Performance.

Die Charakterisierung serieller Verbindungen einschließlich der Analyse von S-Parametern, der Übertragungsfunktion und der jeweiligen Impulsantwort bietet einen ganzheitlichen Überblick über die Leistung Ihres Kanals.

Mit Jitter wird die zeitliche Verzögerung des Schaltzeitpunktes von ICs bezeichnet, Jitter stellt eine Störung da die sich u.a. durch das Schließen der Augendiagramme äußert. Die Berücksichtigung verschiedener Arten von Jitter (deterministischer Jitter, zufälliger Jitter) sowohl im Sende- (TX) als auch im Empfangspfad (RX) stellt sicher, dass Ihr Design Jitter tolerieren und die Signalintegrität aufrechterhalten kann.

Die Visualisierung von Augendiagrammen und Bathtub (Badewannen)-Kurven ermöglicht eine präzise Beurteilung der Übertragungsqualität und Zuverlässigkeit.

Die unkomplizierte Parametrisierung der AMI-Modellparameter beschleunigt Ihren Simulationsprozess und erhöht die Nutzerfreundlichkeit.

Durch die Messung der Augenöffnungen und des Signal-Rausch-Verhältnisses (SNR) können Sie die Signalqualität quantifizieren und die Fehlertoleranz der Übertragung bewerten, um so sicherzustellen, dass Ihr Design die Leistungsanforderungen erfüllt.

Related Resources

Dieser Vortrag ist keine Einführung in die DDR4-Technologie, sondern zeigt die Vorgehensweise bei der Implementierung von DDR4-Speicherschnittstellen mit Zuken CR-8000 von der Konzeptionsphase bis zur physischen Platzierung und Verlegung sowie der Validierung für SI und PI.

Am Beispiel der Analyse von SerDes Übertragungsstrecken wie PCI-Express, SATA oder USB3 erläutert unser Experte Ralf Brüning die Methodik einer Analyse- und Constraint-gesteuerten Baugruppenentwicklung mit CR-8000 Design Force.

Der Trend zu Anwendungen mit geringerem Stromverbrauch stellt Leiterplattendesigner vor neue Herausforderungen. Die engen Toleranzen für Timing und Spannung erfordern einen ganzheitlichen Entwurfsansatz, der High Speed Constraining und integrierte Analyseschritte zur Einhaltung der verschiedenen Entwurfsregeln verbindet.

In dieser Präsentation werden die Vor- und Nachteile der verschiedenen Simulationswerkzeuge sowie die Motivation für deren Einsatz im PCB-Entwurfsprozess vorgestellt.

Related Blog Posts

To keep a good high-speed signal quality from driver to receiver on a PCB is not an easy task for designers. One of the most challenging issues is managing the propagation delay and relative time delay mismatches. Let me take you through the process...

Wussten Sie, dass der Ausdruck "Übersprechen" (engl. Crosstalk) aus der Zeit der Telefonzentralen stammt, in denen Mitarbeiter Anrufer miteinander verbunden haben, die manchmal ungewollt das Gespräch eines anderen hören konnten? Man sprach im wahrsten Sinne des Wortes über eine andere Leitung hinweg.

In part 1 of this blog we took a back-to-basics approach and discussed line impedance and its effects in signal integrity. As every electrical conductor comprises capacitance, an inductance, and a frequency-dependent ohmic resistance, and with increasing frequencies, these electrical characteristics will influence and distort the signal.

Impedance and impedance control belong to the oldest and most often discussed topics in PCB design. They are especially important with the high-speed design when related to signal integrity. In this, the first of a two-part blog, we’ll go back to the basics of impedance/impedance control and consider what influences line impedance. In part two, we’ll set about controlling it.

Tips for when routing differential pairs - You can tell when something isn’t as clear as it should be. The same questions come up time and again. You ask three experts and get three different answers. Routing differential pairs can be like that. Why? Because “it depends” - on exactly what signals those pairs are carrying and what kind of PCB you’re creating.

Eine leistungsstarke Simulations- und Analyseumgebung für die die Überprüfung und Analyse von "Was-wäre-wenn-Szenarien" aus Schaltplan- und aus Layoutdaten.

Sind Sie auf der Suche nach einem Werkzeug, das es Ihnen ermöglicht, die EMV Anforderungen für Ihre Produkte zu erfüllen? Dann ist EMC-Adviser EX genau die richtige Lösung für Sie!

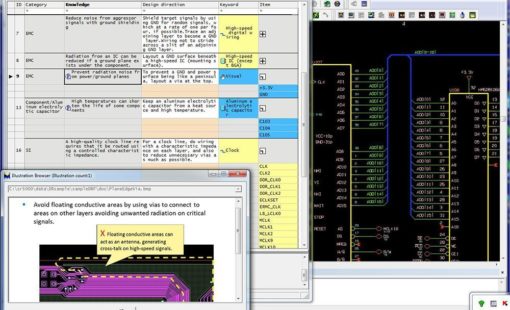

CR-8000 Circuit DR Navi hilft Design-Teams, technisches Fachwissen und PCB Design Best Practices in einer zentralen Datenbank zu bündeln, die in den Designprozess eingebunden ist.

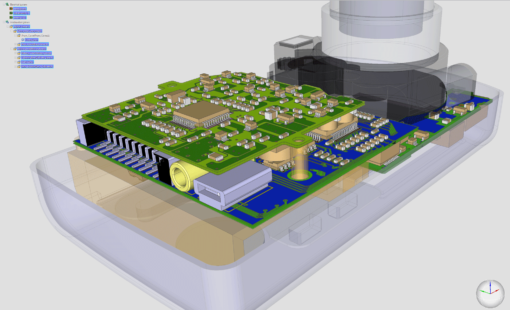

Design Force kombiniert konventionelles 2D-Design mit nativem 3D-Design und den neuesten Technologien in Benutzeroberfläche und Grafik für schnellstes Rendern und Aktualisieren.