Auswahl und Konfiguration aus 42 Regeln in 6 Kategorien

Sind Sie auf der Suche nach einem Werkzeug, das es Ihnen ermöglicht ein EMV-gerechtes Layout von Leiterplatten zu erstellen? Dann ist EMC-Adviser EX genau die richtige Lösung für Sie! Der Einsatz erleichtert die Identifizierung von Problemen mit EMV und Signalintegrität in einer frühen Designphase mit erheblich weniger Aufwand im Vergleich zu manuellen Prüfungen.

Auswahl und Konfiguration aus 42 Regeln in 6 Kategorien

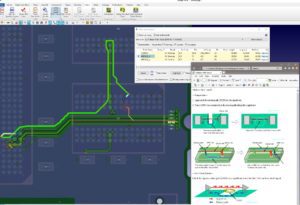

Cross-Probe und Highlight innerhalb des Designs

Berichte und Reports als MS-Excel Dokumente erstellen und freigeben

Der Schaltungsentwickler kann bereits bei der Schaltplanentwicklung EMV-relevante Signale klassifizieren. Die geeigneten EMV Regeln werden für die Anwendung ausgewählt und während der Entwurfsphase angewendet, wie z.B. eine DRC-Prüfung.

Die Richtlinien des EMC Advisers für Design Force enthalten Empfehlungen für Designfragen, die es auch Nicht-Experten ermöglichen, Probleme mit Signalintegrität, Power Integrity und der Elektromagnetischen Verträglichkeit zu lösen und so ein fehlerfreies Layout zu entwickeln.

Benutzer können aus Regelprüfungen (Design Rule Checks) aus 42 Regeln in 6 Kategorien auswählen und konfigurieren, Prüfergebnisse generieren, Cross-Selection und Hervorhebungen innerhalb des PCB Layouts vornehmen und Berichte erstellen.

Zusammenfassende Berichte mit Bildern und Fortschrittsstatus können als Excel-Dokumente zwischen den Mitgliedern des Entwicklungsteams ausgetauscht werden. Es ist keine zusätzliche Software erforderlich, um die identifizierten EMV Probleme zu überprüfen.

Design Rule Checks

EMC Adviser EX kann von folgenden Produkten gestartet werden

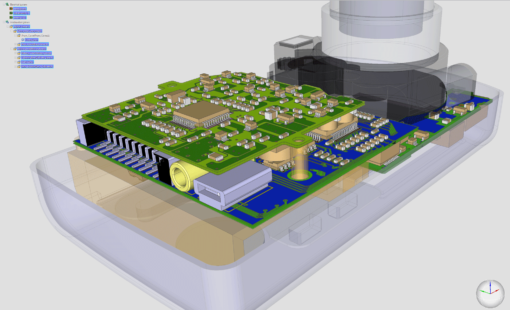

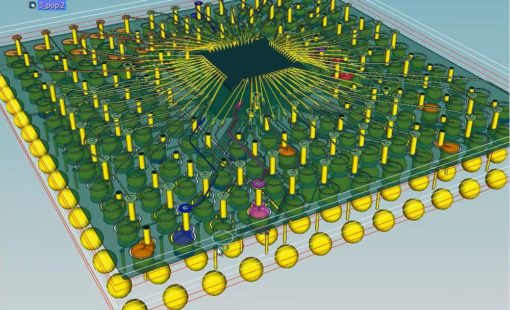

Design Force kombiniert konventionelles 2D-Design mit nativem 3D-Design und den neuesten Technologien in Benutzeroberfläche und Grafik für schnellstes Rendern und Aktualisieren.

Zusätzlich zum Multi-Board PCB Design unterstützt Design Force auch die Entwicklung von IC Packages für Wire-Bond, Flip-Chip und High-Density Advanced Packaging

Aktuelle EMC Adviser EX Blog Posts

EMV Probleme sind in der Leiterplatten-Konstruktionspraxis oft dafür verantwortlich, dass Re-Design-Zyklen notwendig werden. Aufgrund von immer kürzer Innovationszyklen von z.B. Mobiltelefonen oder IoT Applikationen wie Fitness-Trackern und vielen weiteren Elektronikprodukten sind diese zeitintensiven Re-Design-Zyklen unbedingt zu vermeiden.

Wussten Sie, dass der Ausdruck "Übersprechen" (engl. Crosstalk) aus der Zeit der Telefonzentralen stammt, in denen Mitarbeiter Anrufer miteinander verbunden haben, die manchmal ungewollt das Gespräch eines anderen hören konnten? Man sprach im wahrsten Sinne des Wortes über eine andere Leitung hinweg.

In part 1 of this blog we took a back-to-basics approach and discussed line impedance and its effects in signal integrity. As every electrical conductor comprises capacitance, an inductance, and a frequency-dependent ohmic resistance, and with increasing frequencies, these electrical characteristics will influence and distort the signal.