On-demand Webinar

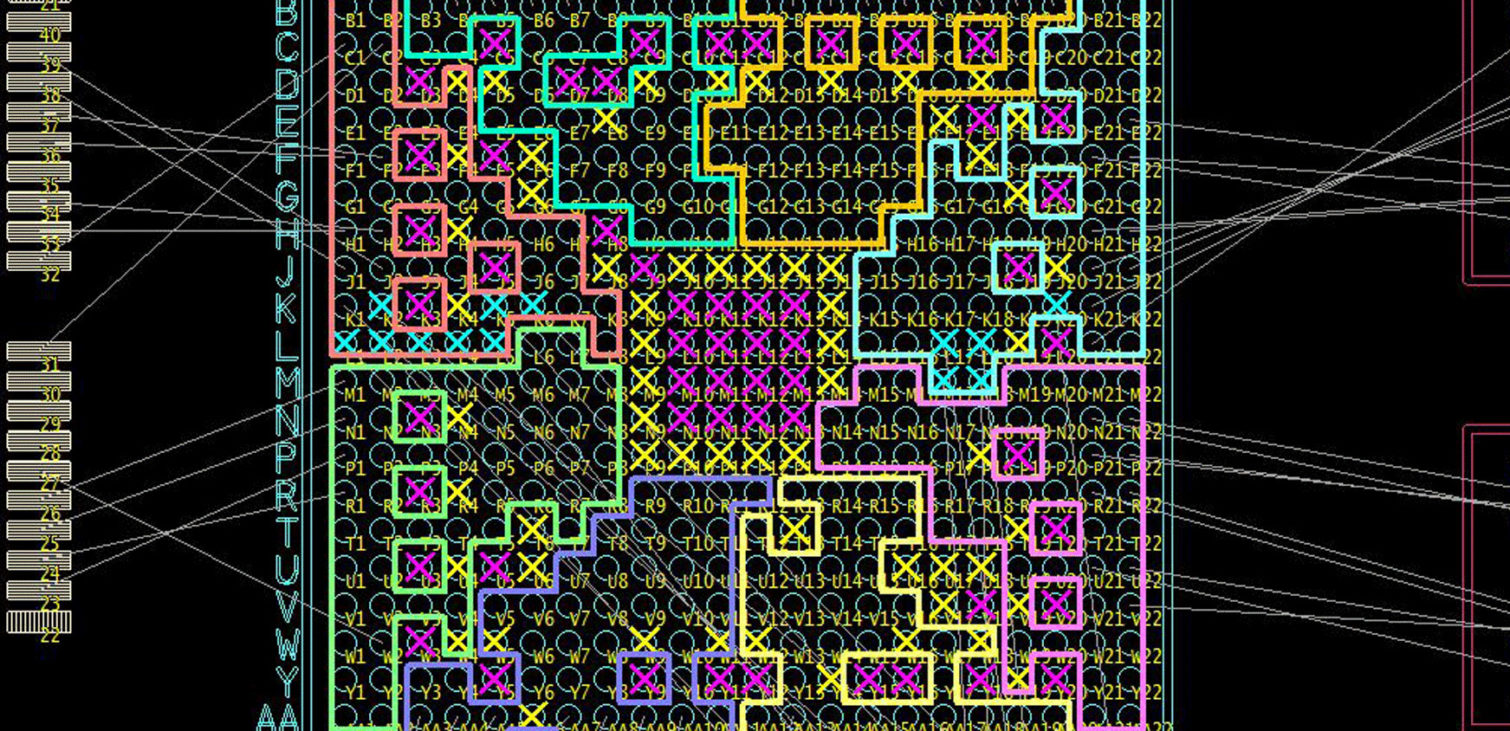

FPGA-Pinzuordnungen ohne Berücksichtigung von Bauteilplatzierung und Routing können nicht nur das Timing beeinflussen, sondern auch die Leiterplatte unroutbar machen. Dieses Webinar zeigt eine effektive FPGA/PCB Co-Design-Umgebung unter Verwendung der neuesten Komponenten von FPGA-Anbietern wie Xilinx, Altera, Lattice und Microsemi. Designteams werden in die Lage versetzt, I/O- und Constraint-Informationen auf FPGAs oder anderen High-Pin-Count-Geräten während des Designprozesses problemlos und jederzeit zu kommunizieren.

Das Webinar betrachtet verschiedene Punkte im Designfluss, an denen das Co-Design des FPGA oder anderer programmierbarer Geräte und des Board-Layouts stattfinden kann; dazu gehören die Erstellung von Bibliothekseinträgen, die Schaltplanerfassung, die I/O-Optimierung und das Pinbelegungs-Management während des Board-Layouts. Mit diesen Maßnahmen verbessern Sie Ihren Designprozess und die Entwicklung programmierbarer Geräte parallel zum PCB-Design, indem Sie unnötige Design-Iterationen vermeiden.

Inhalt – in englischer Sprache

- So optimieren Sie Ihre FPGA-Pinbelegung für das PCB-Design

- FPGA-Design-Daten mit Layoutern in einem automatisierten, fehlerfreien Verfahren austauschen.

- Weitergabe der für das PCB-Layout erforderlichen Konnektivität und Pinbelegung an FPGA-Designer

- Unnötige Design-Iterationen vermeiden und den manuellen Informationsaustausch vermeiden durch Datensynchronisation zwischen FPGA-, PCB- und Schaltplandaten

Zielgruppe

- Entwicklungsleiter, Hardware-Entwickler, FPGA-Entwickler, PCB-Layouter

Dauer

- 36 Minuten