Release 2018 von CR-8000 steigert die Prozess-Effizienz in der PCB-Systementwicklung

Signalspezifische Design-Regeln und differenzierte automatikunterstütze Platzierungs- und Entflechtungshilfen helfen beim Einhalten von Vorgaben hinsichtlich Signalverhalten, Qualität und Fertigbarkeit

11. Juli 2018 – München und Westford (MA), USA – Das neue Release 2018 der PCB-Entwicklungsumgebung CR-8000 von Zuken wurde durch eine Vielzahl von Erzeiterungen und Detailverbesserungen aufgewertet, die eine nachhaltige Steigerung der Prozess-Effizienz bei der Entwicklung von anspruchsvollen Leiterplatten-Designs ermöglichen, die insbesondere anspruchsvollen Anwendungen mit hoher Packungsdichte, hohen Signalfrequenzen oder hohen Spannungen zu Gute kommt.

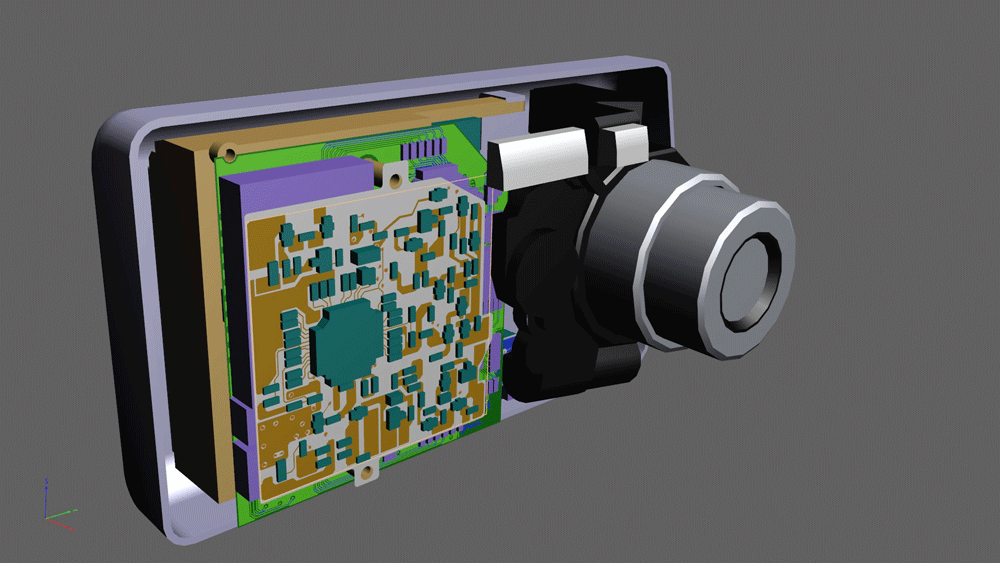

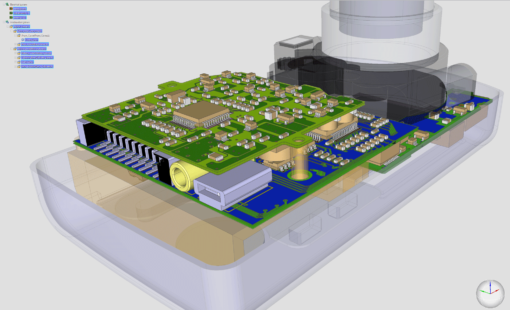

CR-8000 ist eine High-End PCB-Entwicklungsumgebung, die für anspruchvolle Aufgaben im Bereich Systementwicklung und fertigungsgerechte Multi-Board-Implementierung in 2D und 3D konzipiert wurde. CR-8000 umfasst den gesamten PCB Entwicklungszyklus beginnend bei der Planung und Optimierung der Systemarchitektur bis zur Implementierung und Fertigungsausgabe als kohärentes Multi-Board-System, einschließlich des Chip-, Package- und Board-Co-Designs.

Front-Loading durch Spezifikation von Konstruktionsvorgaben

Das Hauptaugenmerk der Erweiterungen von Release 2018 galt der Möglichkeit, differenzierte Vorgaben und Spezifikationen direkt im Stromlaufplan zu hinterlegen und diese in der Konstruktionsphase mit Hilfe von leistungsfähigen Platzierungs- und Entflechtungshilfen zuverlässig umzusetzen. Dadurch wurde eine deutliche Reduktion des Abstimmungsaufwands zwischen Hardware-Entwicklung und Leiterplatten-Konstruktion ermöglicht, wodurch Fehlerrisiken minimiert und die Prozess-Effizienz gesteigert werden konnten.

„Die Kontrolle der PCB-Layouts auf die Einhaltung der wachsenden Anzahl von elektrischen Spezifikationen und Fertigungsvorgaben nimmt bei anspruchsvollen Entwicklungsprojekten einen immer größeren Aufwand in Anspruch, bei dem Hardware-Entwickler und Layout-Konstrukteure gleichermaßen gefordert sind“, erläutert Humair Mandavia, Chief Strategy Officer, Zuken Inc. „Mit den neuen Mechanismen in CR-8000, mit denen diese Vorgaben direkt im Rahmen des Stromlaufplans spezifiziert und umgesetzt werden können, trägt Zuken zu einer erheblichen Reduzierung von Aufwand und Fehlerrisiko bei, was sich letztlich in einer deutlichen Steigerung von Produktivität und Prozesssicherheit niederschlägt.“

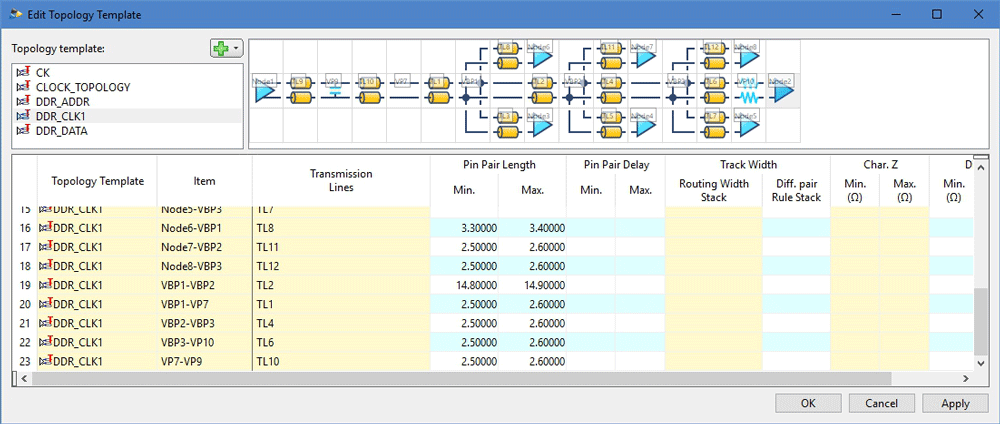

Eine Vorverlagerung von Konstruktionsentscheidungen vom Layout in die Entwicklungsphase – im Fachjargon meist als „Front-Loading“ bezeichnet – konnte durch die Vereinheitlichung der Constraint-Browser von Design Gateway und Design Force erreicht werden. Dadurch sind Hardware-Entwickler jetzt in der Lage, Topologie-Vorgaben, Abstandsregeln und Spezifikationen für die konstruktive Auslegung von Differentialpaaren bereits im Stromlaufplan festzulegen. Vordefinierte Regelsätze (Rule Stacks) können dabei von den Entwicklern aus einer Bibliothek geladen und über einen Rule Stack Editor für spezifische Anforderungen modifiziert werden, so dass trotz Automatisierung und Standardisierung ein hohes Maß an gestalterischer Freiheit gegeben ist. Darüber hinaus können Bestückungsvarianten bereits im Stromlaufplan hinterlegt werden. Dafür steht ein tabellarischer Editor zu Verfügung, über den die Bauteilvarianten ausgewählt und zugewiesen werden können.

Automatisierte Bauteilplatzierung und Entflechtung

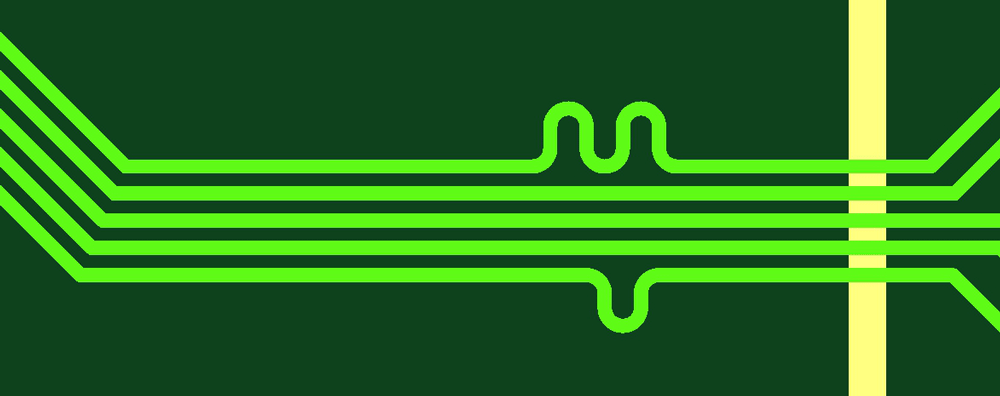

MNeue automatische Funktionen helfen bei der Umsetzung der Entwicklungsvorgaben beim Leiterplanten-Layout: So wird das manuelle Routing von Leiterbahnen durch eine neue Funktion namens Auto-Complete-&-Route ergänzt, mit der Leiterplattenkonstrukteure manuell verlegte Leiterbahnen automatisch vervollständigen können. Bei entsprechender Einstellung kann das Programm auch selbständig zwischen verschiedenen Lagen wechseln. Mit einer neuen Bus-Routing-Funktion können Pfade für Netze mit mehreren Leiterbahnen vorgezeichnet und anschließend automatisch geroutet werden. Die Längen der einzelnen Signale werden dabei automatisch auf die Laufzeitvorgaben des Entwicklers angepasst. Sollten Änderungen an fertig platzierten und gerouteten Boards erforderlich werden, sorgt eine automatische Re-Route-Funktion dafür, dass die Verbindungen zwischen Pins und Leiterbahnen erhalten bleiben, während die Bahnen verschoben werden. Bei allen Operationen werden Spezifikationen und Abstandsvorgaben durch leistungsfähige Algorithmen kontrolliert und korrigiert.

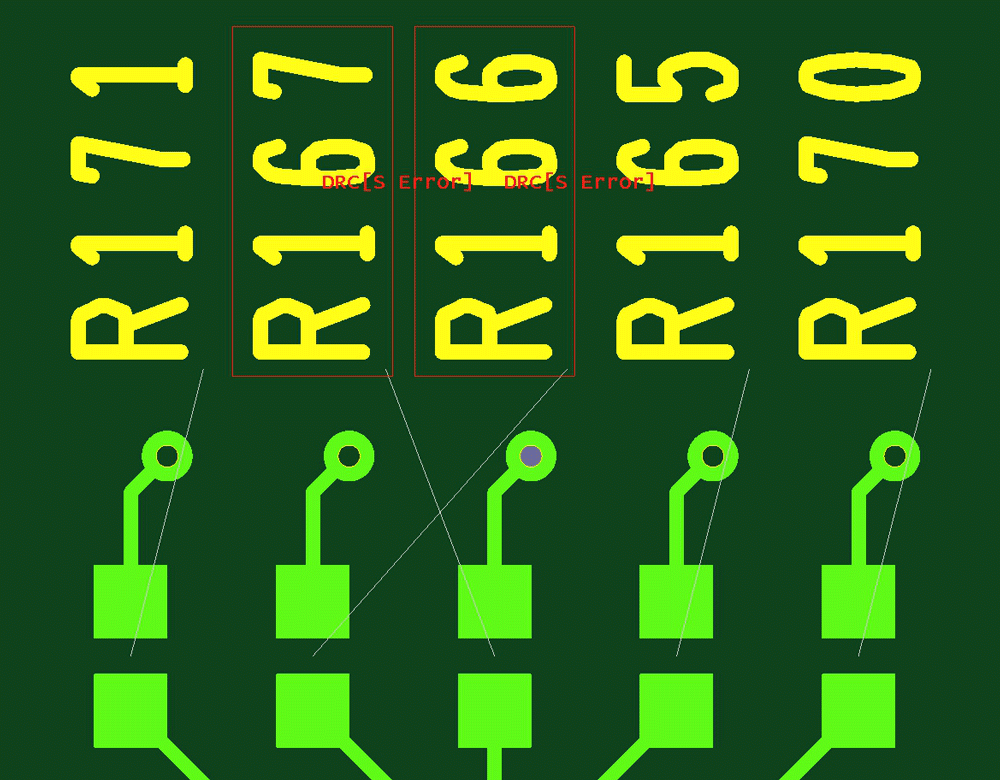

Fertigungsgerechtes Design

Auch fertigungsspezifische Vorgaben, die insbesondere beim High-End-Design berücksichtigt werden müssen, können beim Layout systemunterstützt umgesetzt werden: so können Durchkontaktierungen in Kupferflächen wahlweise nur entlang der Kanten oder innerhalb der Flächen nach definierbarem Muster angeordnet werden. Von den umfangreichen Prüfroutinen vor der Fertigungsfreigabe werden jetzt auch nichtelektrische Elemente wie Silkscreens (Aufdrucke) und Referenzdesignatoren für Montagezeichnungen berücksichtigt, deren Reihenfolge und Zuordnung für die optische Inspektion geprüft und korrigiert werden kann. Durch die Unterstützung des aus dem 3D-Druck stammenden PRC-Formats können mit CR-8000 erzeugte Leiterplattenlayouts jetzt auch mit Standardviewern wie Adobe Acrobat® in 3D dargestellt und inspiziert werden, was vor allem Bearbeitern in der Fertigung zu Gute kommt, die keinen direkten Zugang zur den CR-8000 Autorenwerkzeugen haben.

Related content

- Products

- Products

Design Force kombiniert konventionelles 2D-Design mit nativem 3D-Design und den neuesten Technologien in Benutzeroberfläche und Grafik für schnellstes Rendern und Aktualisieren.

- Products

CR-8000 umfasst eine Suite von Anwendungen, die den gesamten Lebenszyklus des PCB Engineerings abdecken.