- Blog

It’s 25 years since the first FED Conference took place in Berlin back in 1993, as a gathering for the German-speaking electronic and PCB-related industry. This also happened to be the year we consider as the birth of high-speed design.

- Blog

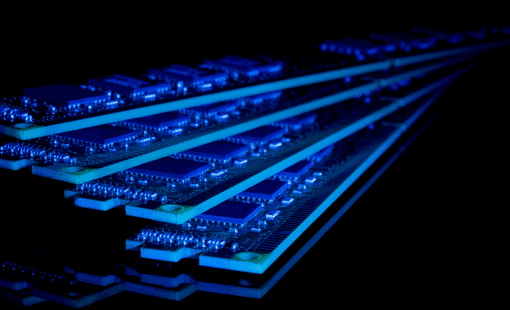

DDR4, the fourth generation of DDR SDRAM technology, is the latest and greatest SDRAM standard and will continue to be until the fifth generation is released. The new standard features a point-to-point architecture that offers superior timing margins.

- Blog

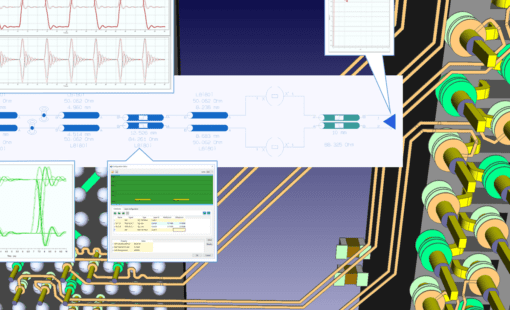

In the final installment of this blog series, you can learn how to use build-up layers and premium FPGAs to deal with the signal integrity challenges arising from high-speed signals in a 3D design capture world.

- Blog

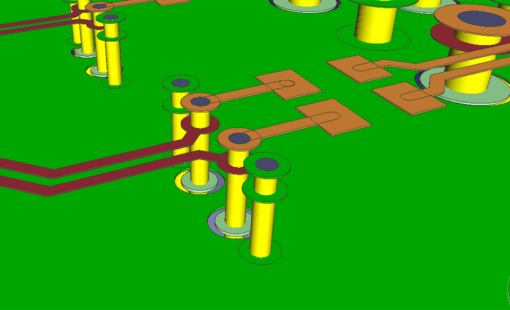

This is the second in my series of blog posts looking at the challenge of maintaining PCB signal integrity with now-common ultra-high speeds and growing adoption of PCB design environments to design in true 3-D. Today I focus on vias and the use of return vias to overcome the issues highlighted in Part 1.

- Blog

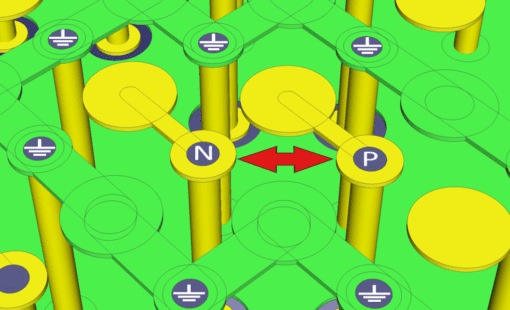

Ultra-high signal speeds demand detailed consideration of the third dimension in PCB design, including via structures and layer stacks. Today I’m going to focus on the challenge. In my two subsequent posts I’ll be reviewing what PCB designers can do to meet that challenge.

- Blog

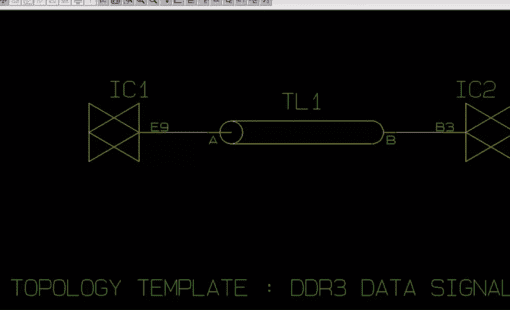

As Zuken technology partners, we are often asked about how best to set PCB constraints for double-data-rate (DDR) memory, and how to route to those constraints. This question arose recently when we were asked to create a common style of DDR3 design for training, and we tried mining the web for detailed information on PCB constraints. There had to be something out there, we thought.

- Blog

Last week I introduced you to the concept of S-Parameters, and now I’m going to explain a bit more about measuring them and simulating with S-Parameter models.

- Blog

I’d like to explain to you in straightforward terms what S-Parameters are and why they’re so useful. When I say “straightforward”, I mean that in a technical sense, but this is a specialised area. If you’re not designing high-speed PCBs, or you don’t know much about signal integrity, you might want to tune out now.