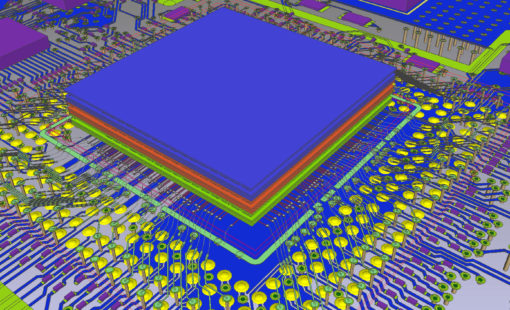

With the utilization of CR-8000 Design Force, Zuken helps to overcome design challenges associated with 3D integration in the pursuit of next-generation semiconductor technologies.

Munich, Allemagne, et Westford, MA, États-Unis, 6 décembre 2022 – Zuken a créé un partenariat avec l’Alliance WOW dirigée par le professeur Takayuki Ohba du Laboratoire de recherche en sciences et technologies de l’Institut de technologie de Tokyo. L’Alliance WOW est une plate-forme de recherche industrielle et universitaire qui réunit diverses parties prenantes, notamment des entreprises, des universités et des instituts de recherche, afin de faire progresser le développement des semi-conducteurs de la prochaine génération basés sur les technologies d’intégration wafer-on-wafer (WOW).

Dirigée par le laboratoire de recherche et de technologie de l’Institut de technologie de Tokyo, l’alliance WOW est activement impliquée dans l’avancement d’une technologie d’intégration de chiplets extrêmement avancée. L’objectif principal de l’alliance est de relever les défis associés à l’intégration 3D, notamment en ce qui concerne la consommation d’énergie, la résistance thermique et l’amélioration des performances, à l’aide d’une solution complète qui permet non seulement de relever ces défis, mais aussi d’améliorer les performances globales des systèmes à semi-conducteurs

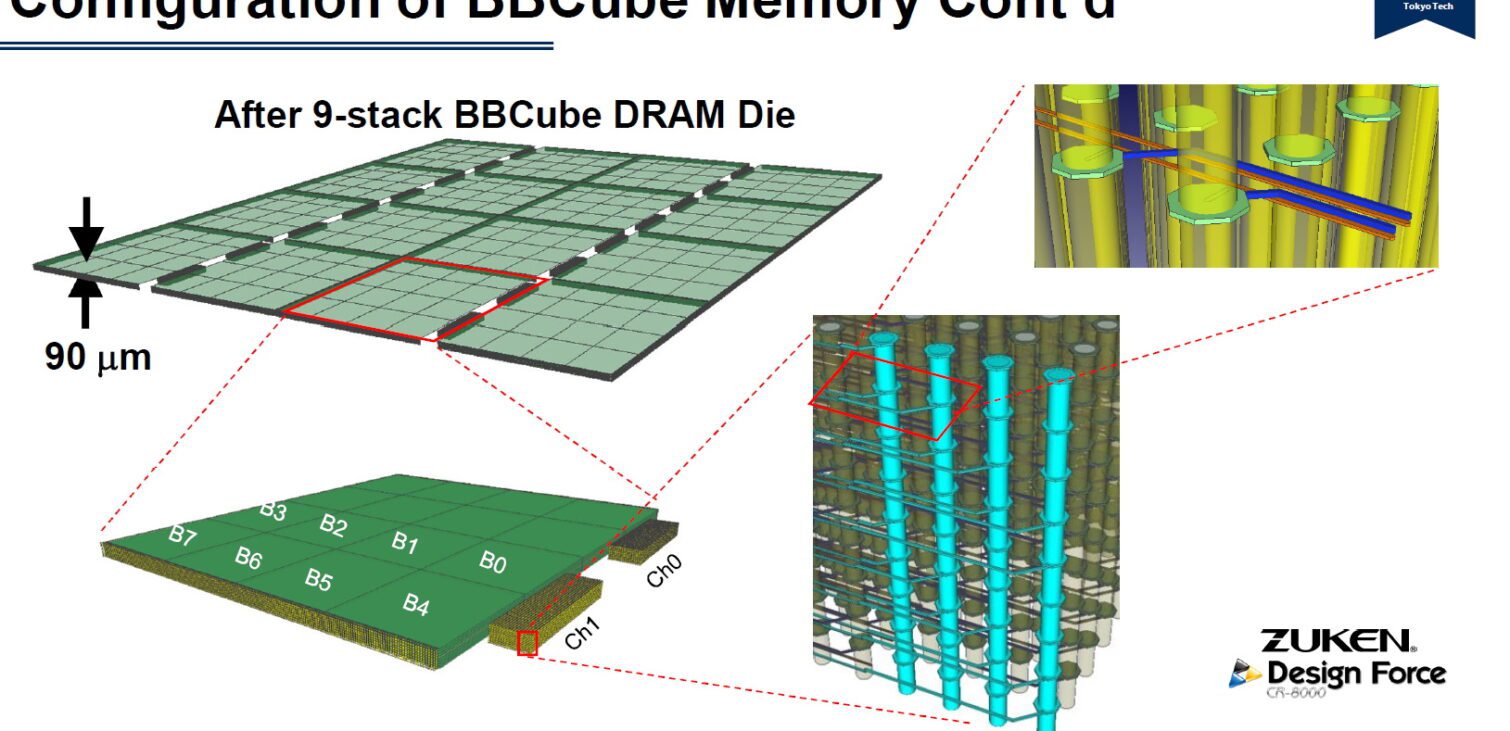

Grâce à ses efforts conjoints avec des partenaires de l’industrie et de la recherche, l’alliance WOW a mis au point une technologie propriétaire de réduction de l’épaisseur des plaquettes de silicium pour remédier aux limites de l’épaisseur conventionnelle des plaquettes de silicium, en la réduisant d’une plage typique de 20-30 μm à une épaisseur ultra-fine de 4 μm. En outre, l’alliance a également mis en œuvre une technologie d’interconnexion TSV (Through-Silicon Via), éliminant le besoin de bosses (“bumps”) traditionnelles. En outre, une transmission à large bande passante au niveau du téraoctet est obtenue grâce à des interconnexions super parallèles à haute densité, permettant l’empilement de wafers dans les configurations WOW (wafer on wafer) et COW (chip on wafer).

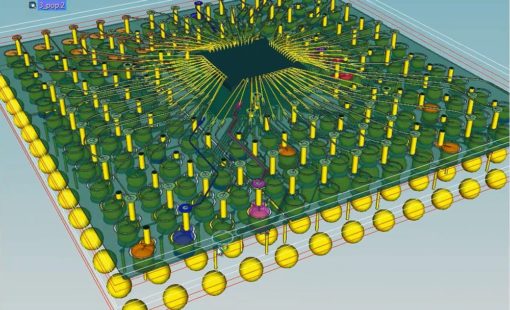

Pour satisfaire aux exigences de conception de la nouvelle technologie, Zuken apporte son environnement de conception multicarte CR-8000 Design Force. Ce puissant outil de conception permet à l’alliance de s’attaquer efficacement aux complexités de l’intégration 3D et de faciliter le processus de conception des circuits intégrés. Pour plus d’informations, veuillez consulter le site WOW Alliance | Takayuki Ohba Laboratory, Laboratory for Future Interdisciplinary Research of Science and Technology, Tokyo Institute of Technology (titech.ac.jp)

L’alliance WOW

Les semi-conducteurs pour processeurs et mémoires, indispensables aux ordinateurs personnels et aux smartphones, ont vu leurs performances augmenter grâce à la réduction de la taille des dispositifs. Toutefois, l’industrie est actuellement confrontée aux limites physiques inhérentes à la technologie conventionnelle pour réduire davantage la taille des composants semi-conducteurs.

Pour surmonter ces contraintes, l’alliance WOW, dirigée par le laboratoire de recherche interdisciplinaire du futur, met au point une technologie d’intégration tridimensionnelle à grande échelle (3D LSI) qui utilise des interconnexions verticales et une technologie sophistiquée de matrices de semi-conducteurs ultra-fines permettant d’améliorer les performances en rendant les matrices plus petites et plus minces.

Grâce à cette technologie, les membres de l’alliance WOW travaillent à l’intégration de plusieurs fonctions de semi-conducteurs dans un seul module, surmontant ainsi les limites inhérentes à la réduction des dispositifs en deux dimensions seulement. Pour plus d’informations, veuillez consulter le site WOW Alliance | Takayuki Ohba Laboratory, Laboratory for Future Interdisciplinary Research of Science and Technology, Tokyo Institute of Technology (titech.ac.jp)

Related Content

- Products

Design Force offers an intuitive, integrated environment for designing single and multi-die packages for wire-bond, flip-chip, and high density advanced packaging.

- Products