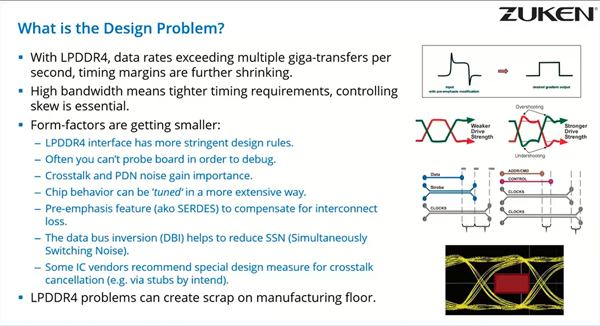

The ongoing trend to lower power applications across all industry segments (driven by mobile devices, but now being used in wider industry segments like automotive and industrial automation) has created new design challenges for PCB designers.

Governed by the framework of the JEDEC standard JESD209-4C, the relevant rules and constraints for LPDDR4 memory devices and their usage have been adopted by all semiconductor vendors. The tight timing and voltage margins require a holistic design approach combining high-speed constraining and integrated analysis steps ensuring the various design rules.

In this presentation you will be introduced to the necessary steps in constraining and validation of LPDDR4 on the basis of a real design realized in CR-8000 Design Force right first time.

What to expect

- Background, definitions and introduction

- Background of memory evolution

- What is LPDDR4?

- Impact of narrowing voltage power further down

- Implementing LPDDR4

- Design constraints of LPDDR4 and how to implement

- Meaning of JEDEC compliance, IC vendor compliance and role of signal and power integrity

- Designing LPDDR4 memory systems in CR-8000 Design Force

- Outlook for future memory systems

Presenter

Ralf Bruening

Product Manager and Senior Consultant

High Speed Design Solutions

Zuken GmbH, EMC Technology Center

Germany

Ralf Bruening is a product manager involved in development and deployment of Zuken’s analysis and high-speed solutions for the past 20 years. Ralf works to improve customer design processes and solve complex technical challenges associated with high speed signal transmission, power integrity problems and EMI emissions. In his free time, Ralf likes to golf, cook for his family and listen to rock music.