This is my second of two posts that look at why PCB designers should take on more of an active role in signal integrity screening and the benefits for the organization – here’s the first part.

Signal Integrity Screening by PCB Designer – but thats more work for ME???

Why would you as a PCB designer take on this task of signal integrity screening?

Clearly, I am suggesting adding to your already compressed schedule – I can’t deny that fact. And by performing this action, we are departing from traditional placement and routing activities. But hold on, before you switch off – when proposing this action to designers, some have actively told me that they want to increase their value in the design process. Others desire a better understanding of the effects of their routing choices, and a few totally embraced the idea on its own merits – the overall time and money savings for the organization.

Again, you as a PCB designer are best positioned to perform the signal integrity screening, as you are the most intimate with the physical realization, knowing which signal names correspond to which traces. You already have the design environment open and therefore the screening activity simply becomes an extension of what you are already doing – realizing the PCB.

You might be wondering, if design tools are so sophisticated in realizing electrical design intent, why would screening need to take place at all? Give me a minute to explain this one. For crosstalk or multi-drop nets with min/max delays (as opposed to lengths), often it is easier to route nets first without considering constraints and then resolve issues using manual or automated methods. Resolving min/max delay issues requires multiple passes. For the first pass, a faster calculation mode is used to check delay of each branch. Then at screening time, actual simulation is used to incorporate all of the reflections and logic low and high voltage levels. Screening for overshoot is best performed after placement. At this stage, the design is returned to the engineer with nets flagged that require termination. Therefore, signal integrity screening is really a continual process throughout the board layout phase.

Steps for a PCB Designer to implement Signal Integrity (SI) Screening

Let us get specific about your actions when performing signal integrity screening using Zuken’s CR-5000 Lightning solution as an example.

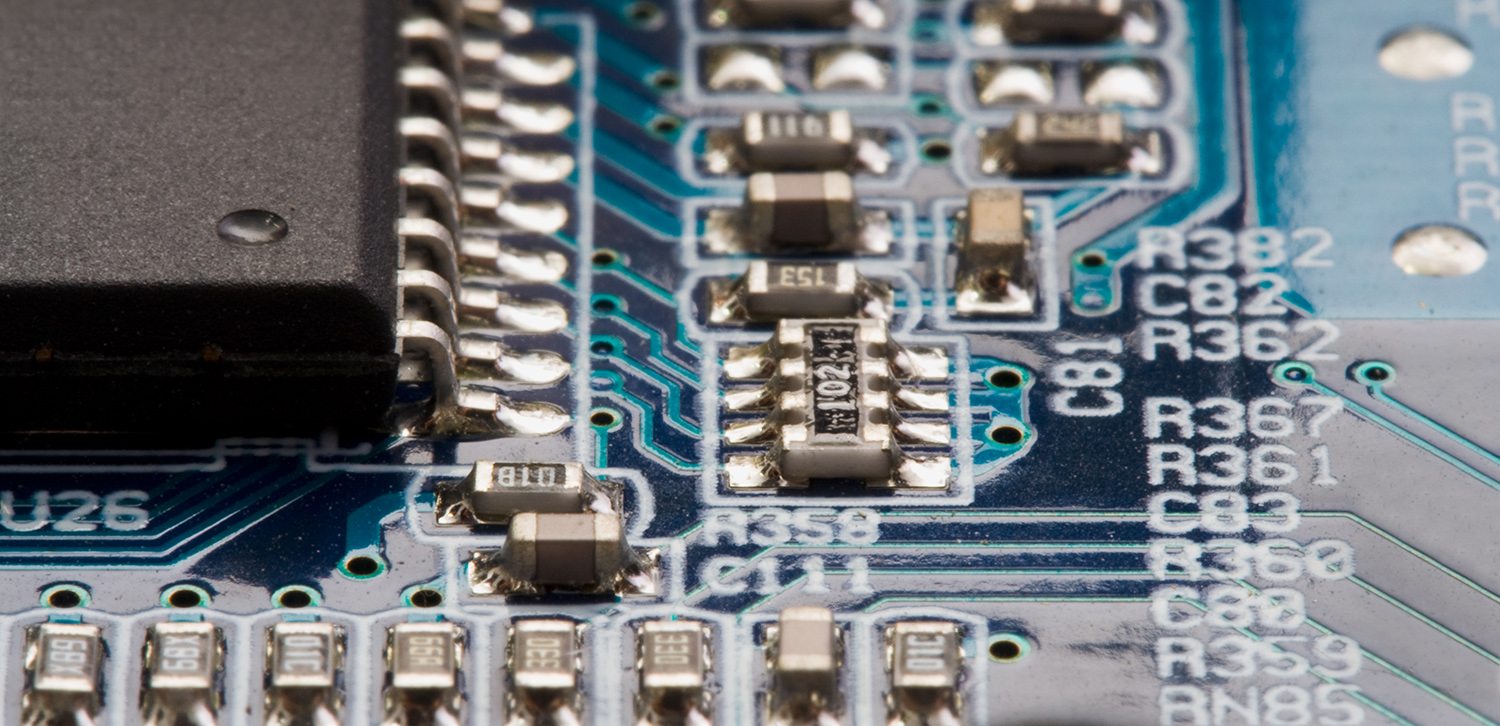

Confirm Board Stackup: A first step is for you to confirm the board stackup, ensuring that the materials, thicknesses, and reference planes are correctly established. With this in hand, you create a field solution so that crosstalk and delays can be calculated. In addition, you can assess the characteristic impedance for a set of trace widths or conversely, calculate a set of trace widths based upon specified impedance. A similar process applies to differential signaling, where the variables are trace width, trace-to-trace spacing, and differential impedance. Below is a screenshot of the stackup editor.

Set-up Default Simulation Models: Ideally, the engineer has assembled SI models for the design that were used when he or she experimented with signaling scenarios prior to schematic capture. In this case, assigning models is straightforward.

So you don’t operate in an ideal world? Never fear, if this is not the case, you can specify driver/receiver models that are appropriate for the technology being used.

Assess Constraints: Next, you assess constraints. Ideally (again that utopian word), the engineer has captured the design’s electrical intent (mV of crosstalk and ps of delay) directly within CR-5000 Lightning. In contrast, it may be that the engineer has communicated requirements in documentation; it may be incumbent upon you to enter them. In the absence of specified constraints, for the purposes of SI screening you can constrain the design automatically for crosstalk, overshoot, and stub length based on the rise time of the SI models.

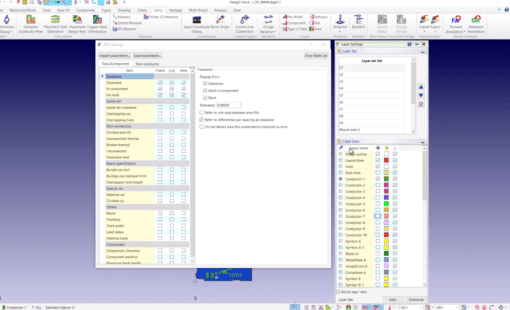

Configure Analysis and Checking: At this point, you configure how the tool will behave when screening is performed. The default settings are shown below. However, if you also want to assess overshoot, the button for Simulation under Signal Integrity would need to be selected. In the Physical Editor, you specify how crosstalk will be reported when checking is performed.

Perform Screening and Review the Results in Constraint Manager: After the board has been placed and there is routing to evaluate, you start the screening process. Results are shown in the spreadsheet-based presentation of the Constraint Manager. To investigate a net of interest, you use the “Update Selected” command. If you choose many nets to review, the color-coded results make it easy to see which nets are in compliance (color green), close to violation (orange) or exceeding the constraint (red). In the crosstalk case, shown below, the contribution of the primary aggressors is included.

If desired, you can check distortion, as shown here:

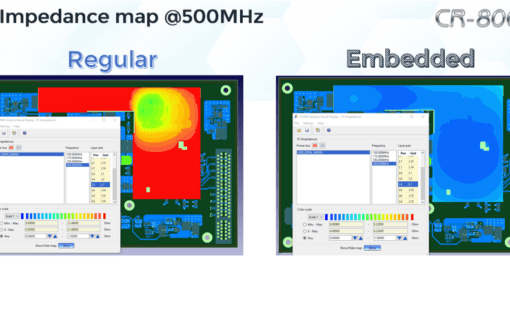

You can also check the impedance of a net based on the layers it traverses.

Finally, you can check delays.

Perform Checking and Review the Results in the Physical Editor: You may choose to review the design on the board itself. To do so, you check the nets or the entire board for crosstalk, and then locate the crosstalk with an interactive command that steps through each crosstalk victim. Here is the display that that you would see:

Resolve Issues and Send Design to the Engineer for Deeper Review: As issues are found, you should resolve them, if possible. When you save the design, any color-coded results will persist in the Constraint Manager window for the engineer to examine more closely.

Conclusions

The practice of creating a high-speed digital design requires that both agents, the electrical engineer and the PCB designer, work even more closely.

The engineer needs to delve into matters that have typically concerned only the designer, such as stackup, trace widths, and spacings, in order to yield the desired characteristic single-ended and differential pair impedances.

You as the designer need to understand that routing for delay is different from routing for length and that signals with faster edge rates create more crosstalk than those with slower edge rates. With that in mind and armed with the proper tools, the designer who performs signal integrity screening during layout significantly improves the overall design process.

You address simple SI issues earlier, freeing up the engineer to focus on tougher problems. This practice can minimize the need for rework and reduce the number of large SI review cycles needed.

All of this means that the product can be delivered earlier with higher quality, thereby saving time and money.

I have used Zuken’s CR-5000 Lightning high-speed design solution to illustrate all the points in this series of blog posts. If you click on this link, you can also download more high-speed design articles from the resulting web page on Zuken.com.

Additionally if you would like some help with your Signal Integrity Processes, take a look at the Consultancy services offered by Zuken in this area.

If you have any questions on signal integrity screening, feel free to post a comment below and I’ll get right back to you.

Related Products and Resources

- Products

Today’s Desktop PCB Design tools require better connectivity to the outside world. eCADSTAR offers a newer level of connectivity that brings users closer to their parts providers than ever before. This allows Engineers to selected parts and drag them directly to their design. Add the additional functionality of high power Signal integrity verification and Power integrity analysis and you have the Ultimate Desktop PCB Engineering solution.

- Products

- Products

Building a competitive product today is much more difficult than a few years ago. Existing PCB-centric design processes are limited to a single PCB and do not provide the necessary tools for today’s competitive product development environment. PCB-centric design processes are falling behind.