Introduction

Over the next few weeks I’m going to talk to you about the high-speed design challenges associated with Low Voltage Differential Signalling (LVDS) and how to overcome them. Today I’ll start by mentioning some applications of LVDS and some basics about how it works. Next week I’ll share my knowledge on effective and efficient PCB routing of LVDS signals.

LVDS is everywhere:

- Serial ATA (SATA)

- RapidIO

- FireWire

- SpaceWire

- HyperTransport

- PCI Express (PCIe)

- USB3 SuperSpeed 4.8GHz and its predecessor USB2

So why is it so popular?

Well LVDS delivers low power combined with high-speed and excellent electromagnetic compatibility (EMC). It’s as simple as that, at least until we get into some detail. Low power has been a hot topic for a long time now and is likely to remain so – not just because it’s thought to stop ice shelves breaking off but because mobile device batteries have an annoying habit of running down (usually just when you are about to send that critical email or make an urgent call).

I don’t know about you, but I read the news on my phone in the coffee house and then I do my mail and surf around a bit. The longer my phone can last without messing around with its micro-USB umbilical cord the less hassle it is to use it.

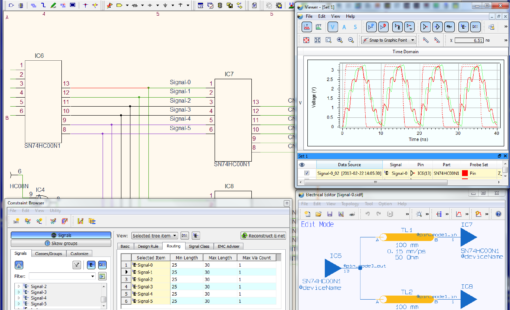

At Zuken Technology Centre (ZTC), Bristol, UK (where I am based), most of the software design work we do concerns printed circuit board (PCB) design: products like CR-5000 Design Gateway (schematic) through physical layout (CR-5000 Board Designer and CR-5000 Lightning) to production data with signal integrity, electromagnetic compatibility (EMC) power integrity and constraint management.

How Does LVDS Work?

LVDS is differential because differential signalling offers much higher bandwidth and noise immunity than single-ended.

LVDS is a current looptechnology. Is that a new idea? Well, no. In fact around the time I started work the 20mA current loop was losing ground to RS232-C as a way to interface Teletypes to mainframes. It wasn’t that long ago: Woodstock and the Apollo 11 lunar landing were a whole two years in the past by then!

The idea of a current loop is simple: The transmitter injects a current that passes through a resistor and because, by Ohm’s Law, V=IR, a voltage is developed across it.

The voltage is the signal at the receiver and that’s why LVDS inputs on FPGAs (field-programmable gate arrays) frequently feature an on-chip 100Ω differential termination (100Ω is the approximate differential impedance on the standard 50Ω (single-ended) impedance boards on which the application notes are based).

PCI Express (PCIe)

Data transmission in LVDS is usually Simplex, which means the data is only transmitted in one direction, from driver to receiver.

When two directions are needed, as in PCI Express, it becomes Dual Simplex, which means you need two differential pairs. In PCI Express, each of these makes one lane.

The popularity of PCI Express and compatible technology such as USB3 is partly due to the clock: instead of being separate, it is encoded within the data stream. That, in turn, means clock-to-data skew issues disappear. With this technique, speed has been traded in return for ease of implementation. You may wish to contrast PCI Express with HyperTransport, which uses a separate clock.

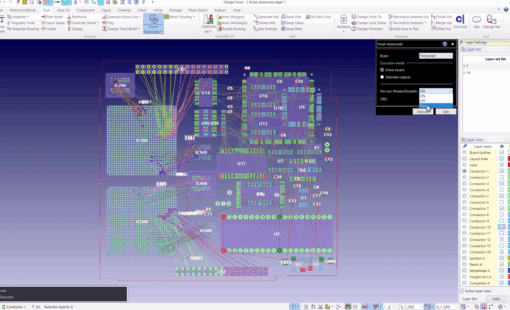

There are often several of these lanes, forming a differential bus; what about skew (length or signal timing difference) between those? Theoretically at least, you only need to match within a data packet interval, so if you use 128-bit data packets, that’s quite a bit of latitude. In practice, symmetry is usually better, especially if the design ever gets modified or the circuit gets re-used. You might decide, for instance, to Trunk Route an eight-lane differential bus; a semi-automatic technique that lets you pick up and route the bus as a single item in real-time. This means that relatively low skew between lanes comes for free in terms of design effort.

Until Next Time

I think that’s enough to absorb for today, but next time I’ll get on to the subject of routing these signals both now and in our super-speed, low-power future. We engineers usually like new things – it’s often what attracted us to engineering in the first place. Driven by our intensely mobile and connected world, I’m sure this will continue and ways will be found to make possible all the products we want, including those we don’t yet know we want – at the speed we want too.

I’d really like to hear from you – what is your experience of working with LVDS? Are there specific design issues that you would like me to cover in my follow-up piece next week on effective and efficient routing of LVDS signals?

Related Products and Resources

- Products

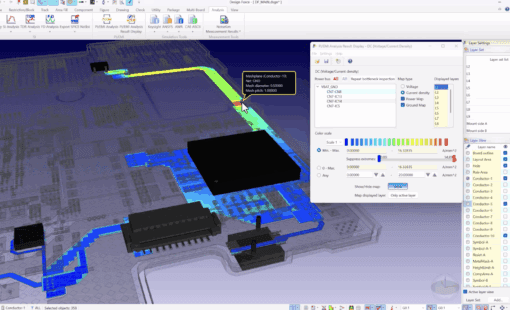

Today’s Desktop PCB Design tools require better connectivity to the outside world. eCADSTAR offers a newer level of connectivity that brings users closer to their parts providers than ever before. This allows Engineers to selected parts and drag them directly to their design. Add the additional functionality of high power Signal integrity verification and Power integrity analysis and you have the Ultimate Desktop PCB Engineering solution.

- Products

- Products

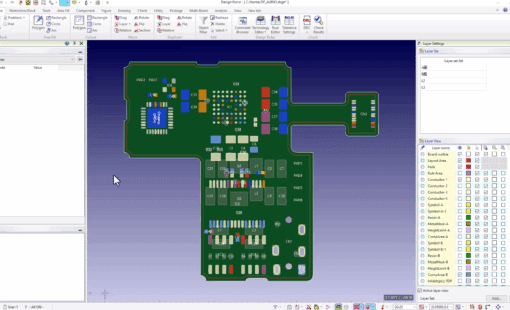

PCB Design Creation - Design Gateway is a platform for logical circuit design and verification of single and multi-board system-level electronic designs. It supports a true system-level circuit design in which individual circuits can be represented and connected as blocks.

- Products

Building a competitive product today is much more difficult than a few years ago. Existing PCB-centric design processes are limited to a single PCB and do not provide the necessary tools for today’s competitive product development environment. PCB-centric design processes are falling behind.