In the first part I covered just the bare essentials of why Low Voltage Differential Signalling (LVDS) is so popular. So what’s important about how these high-speed differential signals are routed, and why?

I’m going to focus here mainly on PCI Express, but the differential routing considerations apply equally to other LVDS technologies and to differential routing in general.

Routing PCI Express

As a reminder, each PCI Express Lane is Dual Simplex, as shown here. Each differential route goes from a differential driver to a differential receiver. There is always a terminator between the + and – sides of the pair, because LVDS is a current loop technology (see Part 1).

So what’s important to consider when routing signals like this?

Recalling from Part 1 that PCI Express encodes clock with data, then skew (differences in route length and delay) between one lane and another isn’t so critical. In technologies that keep the clock separate, like HyperTransport, other types of skew remain a critical consideration.

How about skew between the two simplex differential pairs within each lane? Well it isn’t essential to match transmit and receive within one lane but the inescapable logic of symmetry applies, as for skew between lanes, and the same remedy will work well here.

So we are left with skew within each differential pair. In fact, I don’t like the word “skew” in this case, because a parallel-routed, coupled, differential pair is one signal, not two.

Here again, innovative hardware is taking some of the complication out of routing and in some cases can even adapt to board characteristic impedance variations, compensate for signal loss and introduce delays to compensate for skew.

The Lowest Common Routing Denominator

Whatever signal integrity compensation is included in devices, one exacting routing issue remains; you must match the routing of the two sides of each differential pair precisely. This requirement applies to all multi-gigabit-per-second differential technologies. It isn’t sufficient to match the length of the + and – sides; if it were, then the hardware would be able to compensate. You need to phase-match within a very small tolerance. On one of the point-to-point simplex differential pairs I talked about earlier, you need to start routing at the driver (transmitter) and deviate as little as possible from the recommended track-to-track spacing, making sure the route length from the two driver pins stays as near equal as it is possible to be over the entire length.

The “Differential Impedance” used to calculate the bridge terminating resistor (often on-chip and 100Ω) at the receiver end relies on this precise matching of route length. The impedance is only matched accurately by the terminator when one signal is precisely inverted with respect to the other at every point in the routing; otherwise, the impedance will be different. I will cover mode impedance in a later blog, because it’s a big subject in itself. For now, please take a look at this picture, which represents the field lines between the + and – halves of a differential pair route. Notice how the field lines are pulled together between the two halves. That only happens if the signals are completely complementary and if it doesn’t happen, all bets are off.

For common PCB layer stacks, the application notes for devices such as Field Programmable Gate Arrays (FPGAs) often recommend track-to-track separation within each pair and between one pair and another. It’s very important to maintain these separations and symmetry of items such as vias and test points throughout the routing so that the travelling wave on one side of the pair isn’t altered in a different way from its partner on the other.

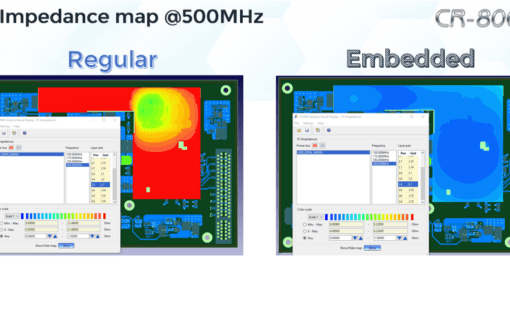

You still need to simulate, because coupling and variations in ground and power planes can easily knock out the intended operation. For high-speed buses like these, it’s usual to simulate eye patterns to make sure the signals behave reliably for a long, pseudo-random data stream.

In Summary

I’ve only skimmed the subject of Gigabit Signalling and LVDS here and I’ve focussed on the lowest common denominator in routing. I’ve not mentioned much about simulation, eye patterns, coupling effects, power integrity and all the rest of that, because I need some material for future blog posts ;-). For now, I need to get back to reading some specifications, so until next time …

Related Products and Resources

- Products

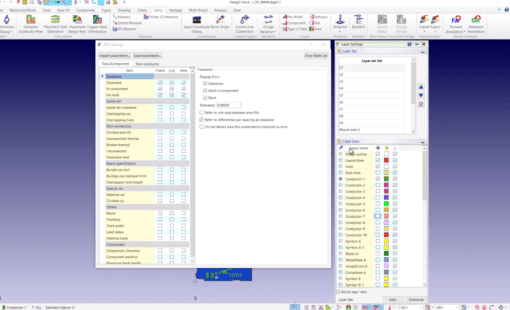

Today’s Desktop PCB Design tools require better connectivity to the outside world. eCADSTAR offers a newer level of connectivity that brings users closer to their parts providers than ever before. This allows Engineers to selected parts and drag them directly to their design. Add the additional functionality of high power Signal integrity verification and Power integrity analysis and you have the Ultimate Desktop PCB Engineering solution.

- Products

- Products

Building a competitive product today is much more difficult than a few years ago. Existing PCB-centric design processes are limited to a single PCB and do not provide the necessary tools for today’s competitive product development environment. PCB-centric design processes are falling behind.