Here’s a new blog post brought to you by Synopsys, focusing on DDR and SI using a combined Synopsys-Zuken flow. This was originally posted by Hélène Thibiéroz on January 23rd, 2014 on the Synopsys’ Blog

Over to Hélène…

You may be tired of hearing only about Mixed-signal verification, so why don’t we switch to signal Integrity? Looking at the recent announcements at CES and Intel’s expected release of server solutions using DDR4 memory later this year, I wanted to further explore this topic. We had a little time ago a very successful webinar that showed in more details DDR capabilities that SI users have and are currently adopting using a combined Synopsys- Zuken flow. Because of our customer testimonies and their enthusiasm on those capabilities, I therefore asked the owners (Griff, Hany) to demo this flow at DesignCon at the ChipHead theatre (see link below) and to talk to us a little more. Our Synopsys WaveView expert Manu V. Pillai is joining the discussion as well to provide more insights on WaveView, which is used by this flow.

Griff Derryberry is an application engineer at Zuken. He focuses on helping customers realize high-speed designs using Zuken’s enterprise PCB solutions.

Manu Velayudhan Pillai has been working with Synopsys Spice simulation tools for over 7 years and currently responsible for Analog/Mixed-signal environment and waveform tool WaveView. He is involved in developing DDR3/DDR4 specific measurements and has been working closely with large companies demonstrating the unique capabilities of WaveWiew for DDR capabilities.

Q1. Griff, can you educate us on the main DDR challenges you are seeing from both a timing and physical design aspect?

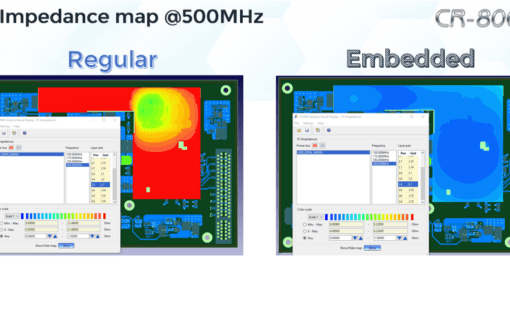

Griff: The main challenges that DDR poses from both timing and physical design aspects includes the need for creating serpentine traces so that setup and hold timing is achieved across a set of nets. This serpentining of traces consumes available real estate, making achieving timing closure more difficult to attain.

Q2. Can you please provide us more insights on the combined Zuken – Synopsys flow you will demo at DesignCon

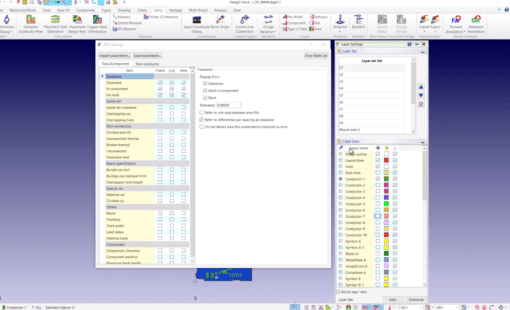

Griff: The Zuken environment provides the design capture, constraint management, and physical realization tools to place and route the DDR system. The Zuken toolset creates the HSPICE netlist containing lossy impedances based on the trace widths and board stackup. HSPICE simulates the result and the timing is validated in Custom WaveView. We will show all aspects of this flow at DesignCon.

Q3. This capability relies heavily on Synopsys Waveform viewer WaveView. Which unique features does WaveView offer for signal integrity?

Manu: Custom WaveView has a powerful EYE diagram measurement tool, which performs basic measurements like height, width, aperture, skew, masks for both transient and STATEYE outputs. The DDR3 specific measurements like derate based setup/hold, tVAC, ringback violations, in Custom WaveView not only generates the reports but also pinpoint the violations in transient signal for further debugging. The built-in Jitter vs Time tool measures pulse-width, periodic, cycle-to-cycle jitter for SI applications. All the measurements can be automated using ACE-TCL scripts and run it in batch-mode hence saving verification time. Overall, a very intuitive and powerful solution.

Q4. There are number of companies showing off their DDR4 memory and Intel is expected to bring out server solutions that use DDR4 memory later this year, are you looking into DDR4 capabilities as well? On a more general scope, which challenges and new features do you see moving forward?

Manu: JEDEC has changed the timing and voltage measurements of DDR4 specifications. The derate based setup/hold measurements in DDR3 are not going to be used in DDR4 and new specification contains Mask based approach which includes deterministic & random jitters. In addition to this DDR4 designs will have a varying Vcent value compared to DDR3 designs.

The upcoming release of Custom WaveView will address the challenges of DDR4 timing and voltage measurements. Waveview measures the Vcent_DQ value, and calculates the eye shifts needed for each DQ pins to get maximum aperture along with other measurements like VdIVW_Total, TdIVW_Total, and SRIN_diVW.

Thanks Griff and Manu for this introduction and Helene for allowing us to share this on the Zuken blog.

Find Zuken at DesignCon

If you’re heading over to Santa Clara for DesignCon, be sure not to miss Griff and Hany’s presentation titled ‘Signal Integrity Analysis of DDR3 High-Speed Memory Interface using HSPICE and Zuken CR-8000 Design Solution’ on Thursday January 30 at 2.50pm in the Chiphead Theatre (session code CT-08).

Related Products and Resources

- Products

Today’s Desktop PCB Design tools require better connectivity to the outside world. eCADSTAR offers a newer level of connectivity that brings users closer to their parts providers than ever before. This allows Engineers to selected parts and drag them directly to their design. Add the additional functionality of high power Signal integrity verification and Power integrity analysis and you have the Ultimate Desktop PCB Engineering solution.

- Products

- Products

Zuken’s engineering data management platform DS-CR has been created to support the specific demands of PCB design data management. It combines multi-site library, design data and configuration management into a unified engineering environment.

- Products

Building a competitive product today is much more difficult than a few years ago. Existing PCB-centric design processes are limited to a single PCB and do not provide the necessary tools for today’s competitive product development environment. PCB-centric design processes are falling behind.