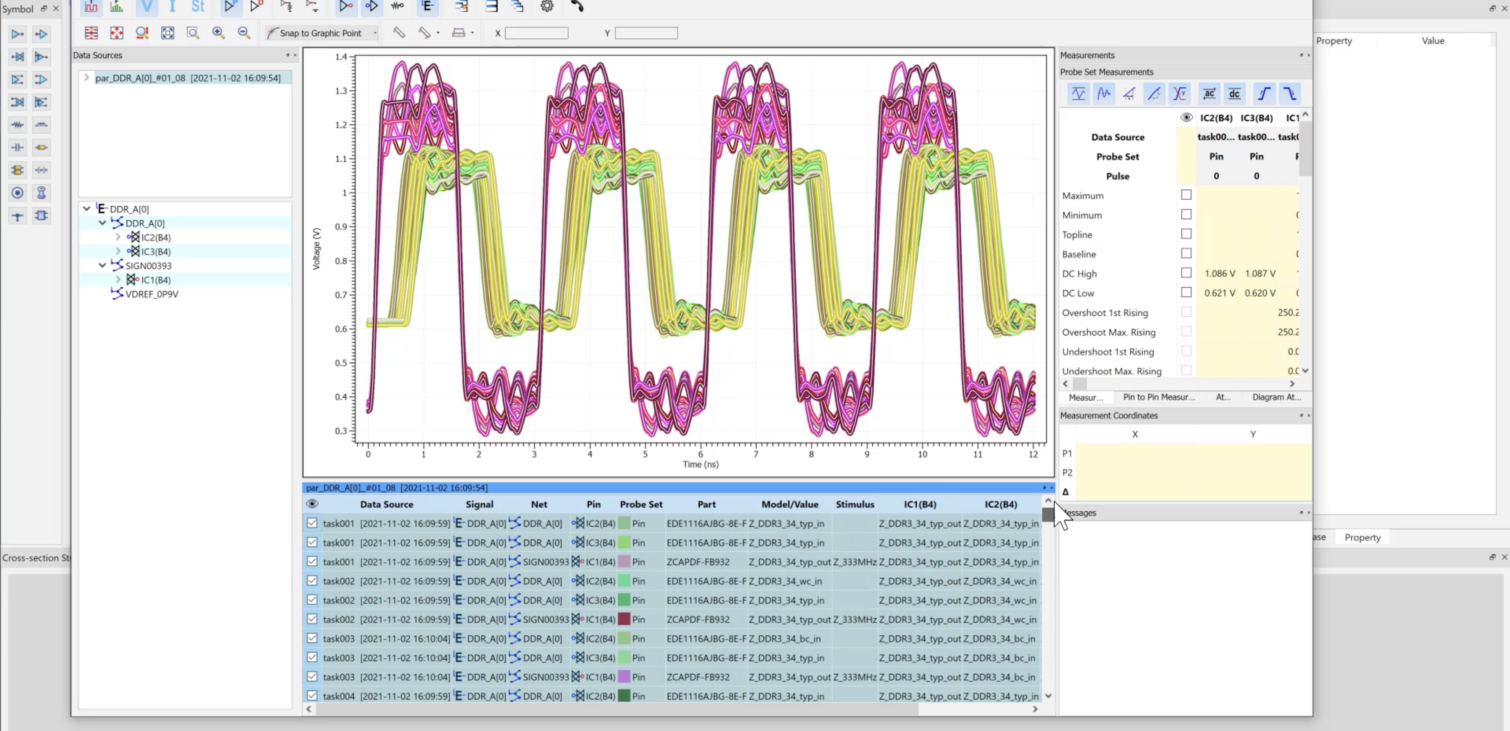

CR-8000 Design Force Signal Integrity tool can now define a buffer Model as a Sweep condition in the Analysis Result Viewer. This option will allow the user to run each model on the same circuit simultaneously and compare the results. When running an analysis on a design users can now simulate the worst-case scenario and compare it to the best case buffer model results at the same time. You can select an existing E-net in your design and open the Electrical Editor, or create your own E-net in the Electrical Editor. In the Electrical Editor select the model you want to run a sweep on and the right mouse button,” Add Sweep items”. Once you have set your sweep parameters you can run the Analysis. The ability to run Parameter sweeps using different Buffer models will make comparing analysis data faster and easier than before.

Below is a video demonstration.

Related Products & Resources

- Webinar

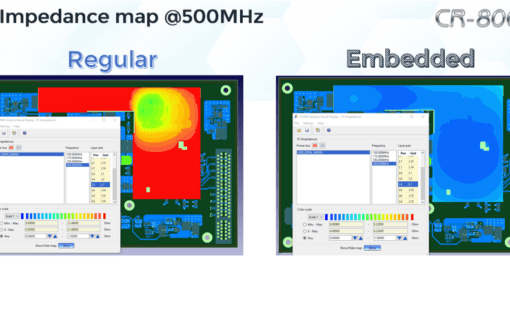

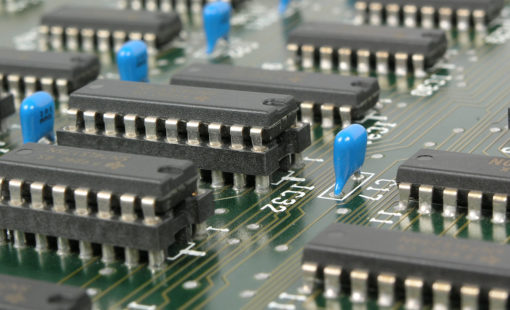

The fast signal switching times of today’s digital systems require particular attention to the signal integrity during design to ensure reliable operation and EMI control.

- Products

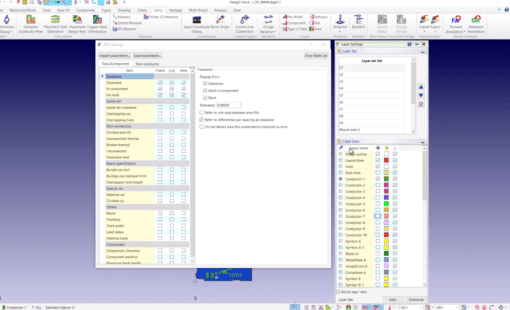

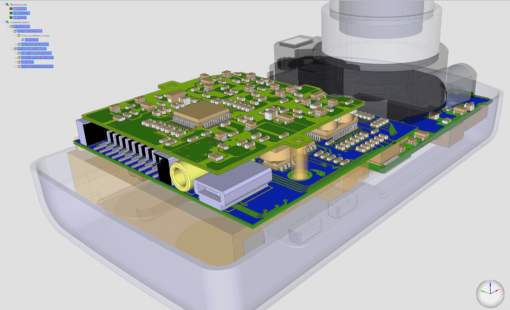

Design Force combines traditional 2D design with native 3D design and the latest human interface techniques, accelerated graphics and almost instantaneous rendering and refreshing. It is the fastest, most effective PCB design solution available today. Design Force enables design teams to layout their designs in the context of a complete system or product.

- Products

Building a competitive product today is much more difficult than a few years ago. Existing PCB-centric design processes are limited to a single PCB and do not provide the necessary tools for today’s competitive product development environment. PCB-centric design processes are falling behind.

- Blog